A process method for increasing ild filling window with adjustable control grid

A process method and control gate technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of increasing the aspect ratio of the unit storage area, difficulty in completely filling the trenches of the unit storage area, and affecting the reliability of the device. Achieve the effect of reducing the aspect ratio, improving the flatness, and the process flow is simple and controllable

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0049] Embodiments embodying the features and advantages of the present invention will be described in detail in the following description. It should be understood that the invention can have various changes in different examples without departing from the scope of the invention, and that the descriptions and illustrations therein are illustrative in nature rather than limiting the invention.

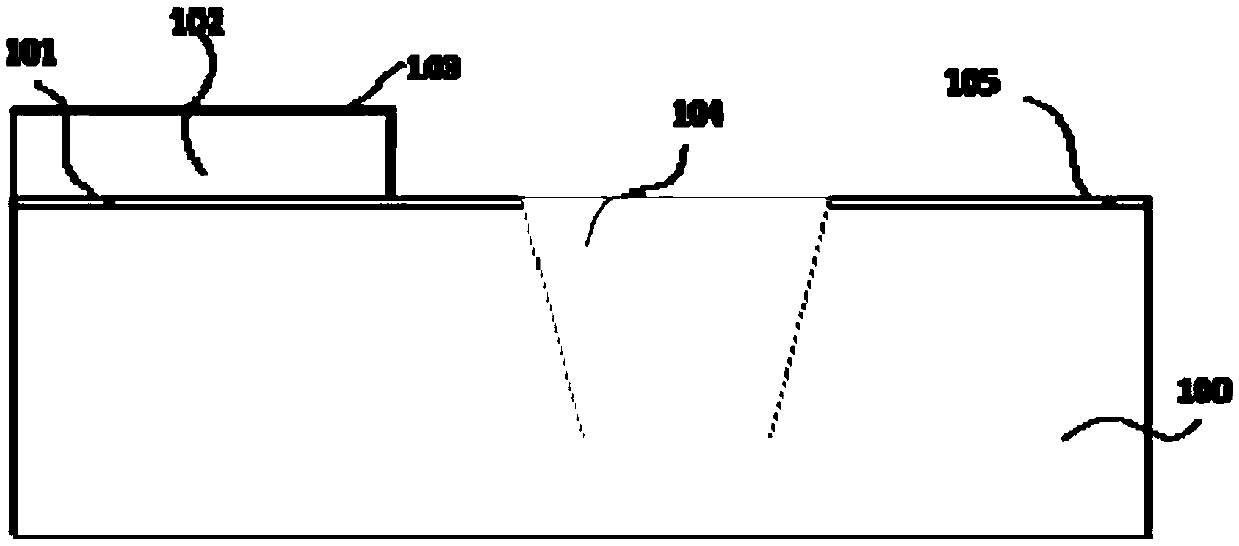

[0050] The process method of increasing the ILD filling window with the adjustable control gate of the present invention will be further described in detail with reference to the accompanying drawings. It should be noted that the problem solved by the present invention is to reduce the thickness of the control gate in the storage area of the unit while maintaining the thicker polysilicon gate layer in the peripheral device area.

[0051] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0052] see Figure...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com