A low-power combined encoding and decoding circuit and encoding and decoding method applied to a network on chip

A network-on-chip, low-power technology, applied in the field of encoding and decoding circuits, can solve the problems of insignificant overall effect, large interconnection network power consumption, high flip rate, etc., to overcome its own area overhead, reduce transmission power consumption, The effect of low dynamic power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

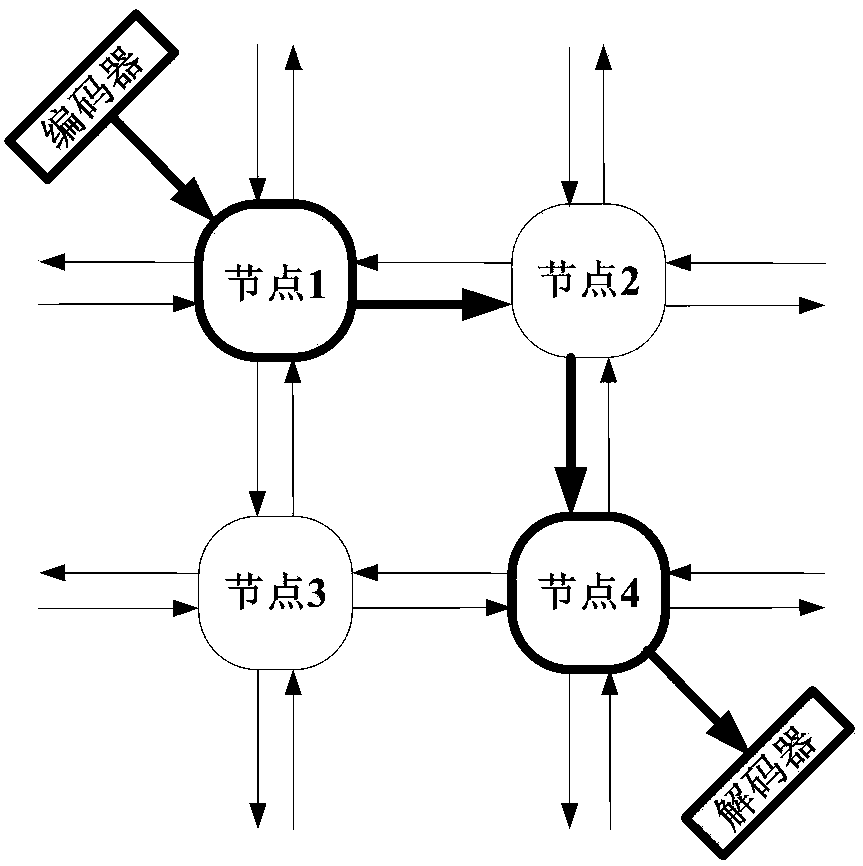

[0044] In this embodiment, the on-chip network is the smallest two-dimensional network of M×N=2×2; and it is used to transmit external data packets; the routing node that receives the data packet is defined as the source node, and the routing node that outputs the data packet is the destination node ;The data packet is composed of n=5 microchips, which are respectively 1 header microchip, n-2=3 individual microchips and 1 tail microchip; each microchip includes a microchip header, a binary microchip counter, a binary packet Counter, low-order data; M and N are integers greater than or equal to 2; n is an integer greater than or equal to 3;

[0045] Such as figure 1 As shown, node 1 is the source node, node 4 is the destination node, a low-power combined encoding and decoding circuit applied to the network on chip, an encoding circuit is set at the input end of the source node, and an encoding circuit is set at the output end of the destination node With decoding circuit;

[...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com