Wafer test pattern yield loss calculation method

A calculation method, wafer testing technology, applied in the direction of semiconductor/solid-state device testing/measurement, etc., can solve the problems of biased judgment results, inability to calculate and analyze the loss rate of test patterns, and labor-intensive problems, so as to achieve the effect of reducing output

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

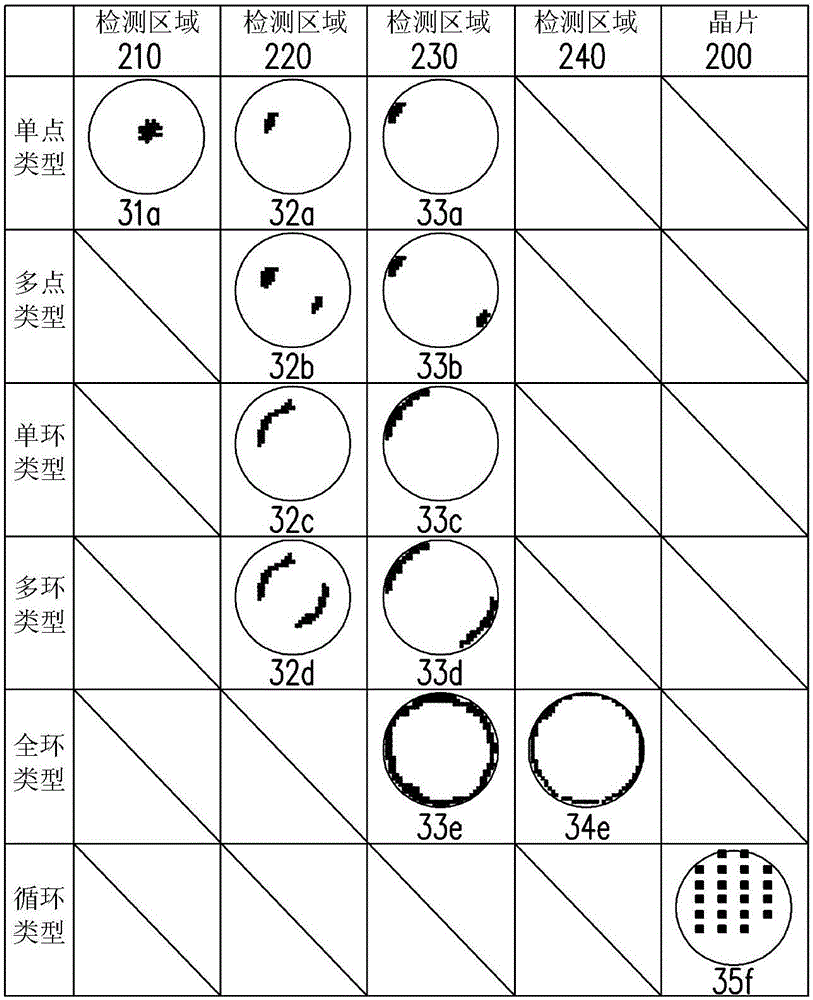

[0034] At present, semiconductor factories still use manual identification to judge the test patterns in the wafer diagram, and it is easy to cause deviations in the judgment results due to different inspection standards of personnel. For this reason, the present invention proposes a method for calculating the loss rate of wafer test patterns, using an electronic device to automatically identify all the test patterns included in the wafer map, and then calculate the loss rate. In order to make the content of the present invention clearer, the following specific examples are given as examples in which the present invention can actually be implemented.

[0035] figure 1 is a block diagram of an electronic device according to an embodiment of the present invention. Please refer to figure 1 , the electronic device 100 includes a processing unit 110 and a storage unit 120 . The storage unit 120 includes a wafer map database 130 and a model database 140 . Here, the processing un...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com