Method for improving memory reliability through fault isolation technology

A fault isolation and reliability technology, applied in static memory, instruments, etc., can solve problems such as system downtime, achieve the effect of preventing downtime, reducing the risk of system downtime, and improving product competitiveness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

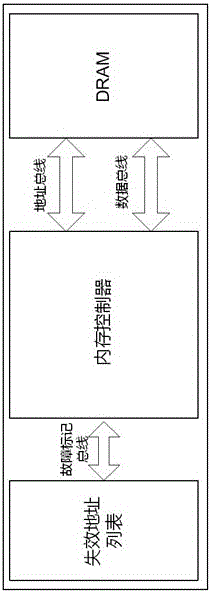

[0021] Such as figure 2 As shown, a method for improving memory reliability through fault isolation technology, said method dynamically adds the Cell address information that is about to go bad during use to the "failure address list" through the test program after the DRAM particles leave the factory In the middle, let the memory controller not access the address space of this piece, thereby prolonging the service life of the memory system, and the economic benefit is obvious.

Embodiment 2

[0023] On the basis of Embodiment 1, the test program described in this embodiment tests all the basic storage cells (Cells) in the DRAM through Refresh refresh charge and discharge, Leakage leakage and other test programs to find out the basic storage cells (Cells) with relatively weak charge retention time ( Cell) to monitor and record the number of errors. When a basic storage unit (Cell) reaches a certain threshold, these error addresses will be marked and isolated to prevent the operating system (OS) from ) to access, so as to achieve the purpose of improving the reliability of the memory system, reduce the risk of system downtime due to memory failure, and have obvious economic benefits.

Embodiment 3

[0025] On the basis of embodiment 2, the method test steps described in the present embodiment are as follows:

[0026] 1) Extend the refresh time of the basic storage unit (Cell), which is longer than the 64ms charge retention time specified in the JEDEC standard, and extend its refresh cycle > 64ms through the memory controller, and those relatively weak cells are in the capacitor after 64ms The charge will leak faster, making it easier to find weaker cell units;

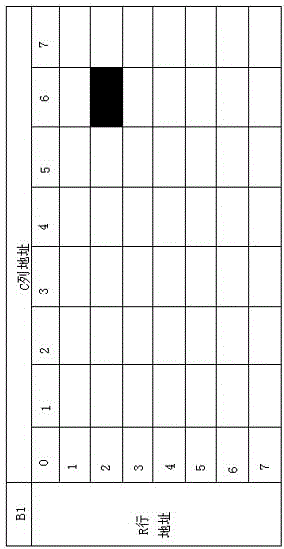

[0027] 2) According to the arrangement order of cells inside the DRAM, by designing a special test mode pattern: set a certain basic storage unit (Cell) to 1, and the surrounding six basic storage units (Cell) to 0, use cell to cell The principle of leakage to find out the weaker cell unit;

[0028] 3) Monitor the problematic basic storage unit (Weak Cell unit) found in the above two tests, and count the number and probability of its long-term error, so as to determine whether it is a random error or a persistent...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com