PSM mode adaptive voltage regulator based on output voltage segmentation

A technology of self-adaptive voltage and output voltage, applied in the direction of adjusting electrical variables, control/regulation systems, instruments, etc., can solve problems such as complex implementation, poor transient response capability, complex circuit implementation, etc., to improve power conversion efficiency, good The effect of transient response characteristics and good transient response capability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

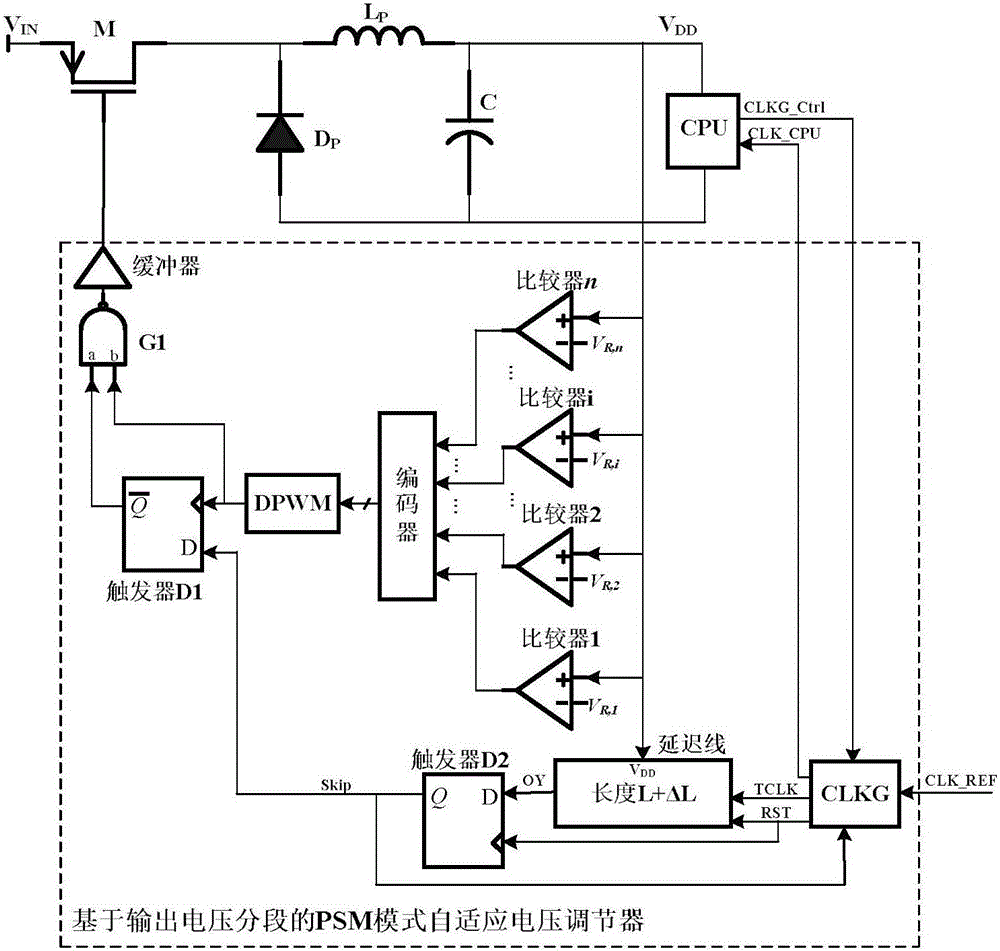

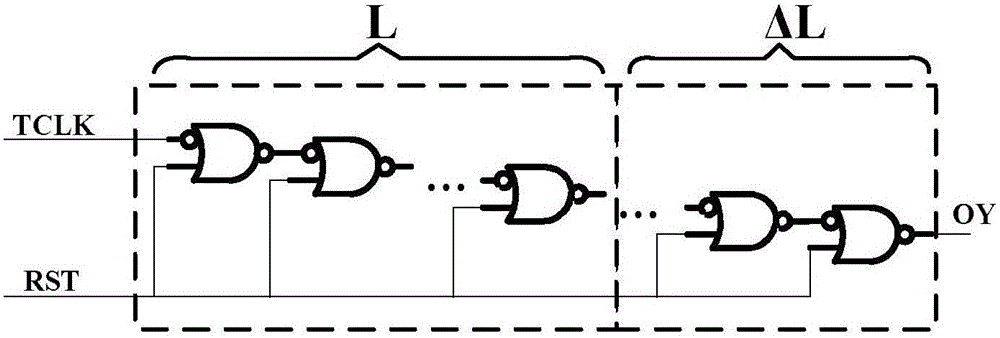

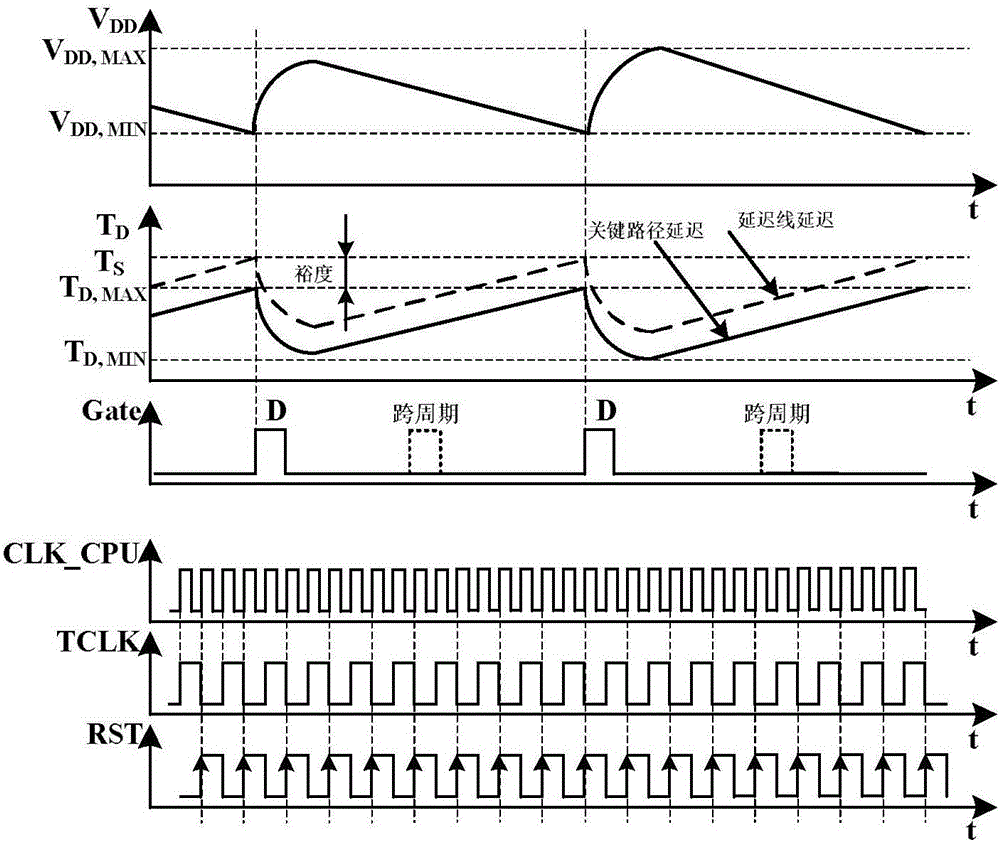

[0022] refer to figure 1 . In the embodiment described below, a PSM mode adaptive voltage regulator based on output voltage segmentation includes a clock signal generator CLKG, a delay line, two flip-flops D1 and D2, n comparators (n is an integer greater than or equal to 1), an encoder, a digital PWM signal generating circuit, a NAND gate G1 and a buffer; wherein, the digital signals output by n comparators are input to the DPWM signal generating circuit after passing through the encoder, The DPWM signal generation circuit will generate pulse signals with different duty ratios and input them to one input terminal of the NAND gate G1, and the output signal of the NAND gate G1 will be acted on by the buffer to control the conduction or cut-off of the main switch tube of the external power converter The clock signal generator CLKG is connected to the trigger D2 through a delay line, and the trigger D2 is connected in series with the trigger D1, and the trigger D1 is electricall...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com