Board-grade multichip joint test action group (JTAG) chain interconnection structure and method

A multi-chip, board-level technology, applied in the field of JTAG, can solve the problems of slow connection and loading, inconvenient production and design maintenance, and affect the efficiency of production, etc., to achieve easy implementation, convenient testing and production maintenance, and convenient use effect of demand

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

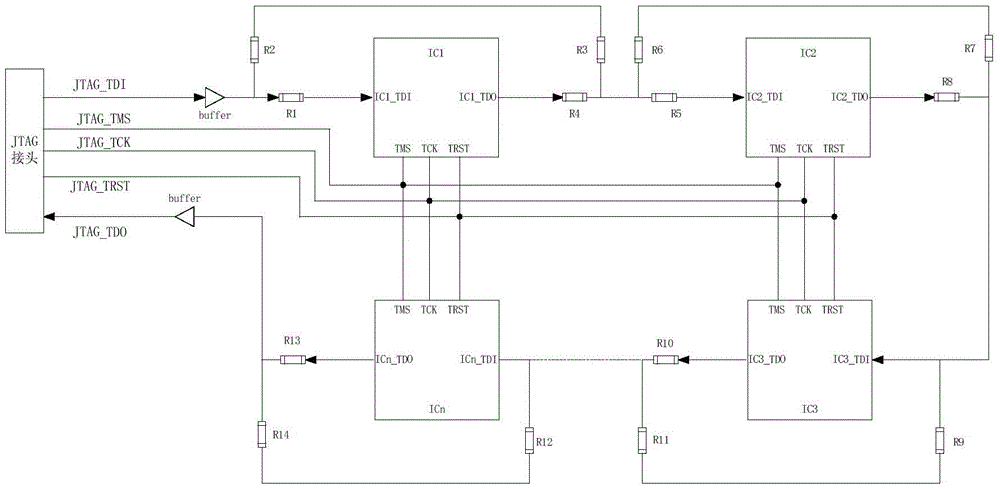

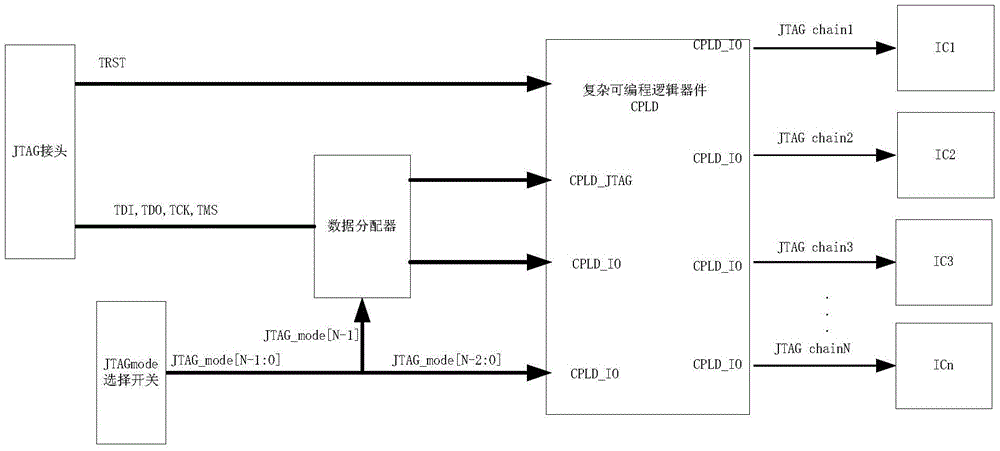

[0035] Such as figure 2 and 4 As shown, the present embodiment discloses a board-level multi-chip JTAG chain interconnection structure, including a JTAG connector and more than one JTAG device, CPLD, data distributor and selection switch; there is a JTAG interface on the CPLD, and the JTAG interface of the CPLD includes a TMS pin, TCK pin, TDI pin, and TDO pin.

[0036] The TMS pin, TCK pin, TDI pin and TDO pin of the JTAG device are respectively connected to the IO port of the CPLD.

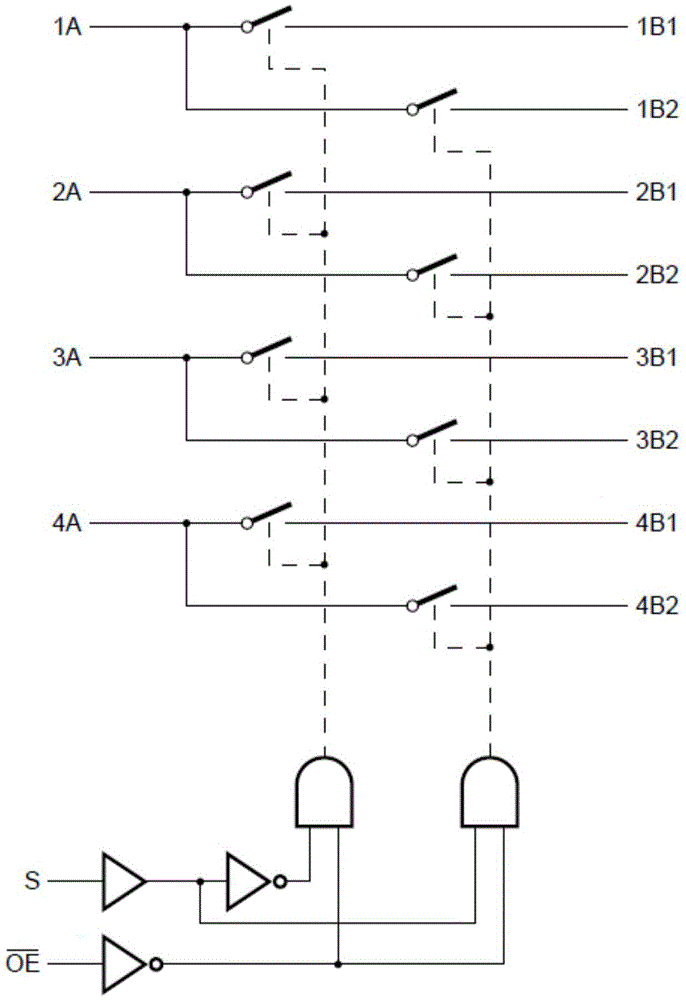

[0037] In this embodiment, the TMS pins, TCK pins, TDI pins and TDO pins of the JTAG connector correspond to the data input terminals connected to the data distributor respectively; The data output end corresponds to the IO port and TMS pin connected to the CPLD respectively, and the data input end of the data distributor connected to the TCK pin of the JTAG connector corresponds to two data output ends respectively corresponding to the IO port and the TCK pin connected to the CPLD; The data...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com