Gate structure forming method and gate structure

A gate structure and gate technology, which is applied in the direction of electrical components, circuits, semiconductor devices, etc., can solve the problem of reduced electrical reliability of the gate dielectric layer, decreased electrical reliability of the gate structure, and increased leakage probability of the gate dielectric layer and other issues, to achieve the effect of increasing electrical stability, reducing the probability of leakage, and reducing the size of MOS devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

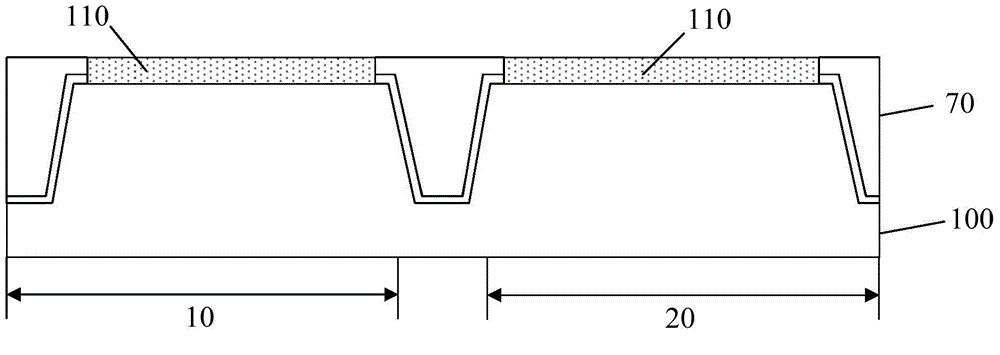

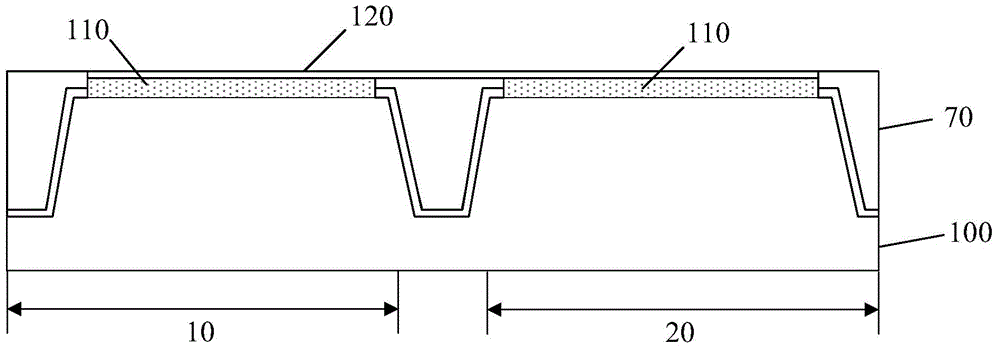

[0047] Taking a semiconductor device including an input / output MOS device and a core MOS device as an example, the voltage value required by the input / output MOS device is generally relatively high, that is to say, the thickness of the gate dielectric layer of the input / output MOS device needs to be adjusted. Larger, but this is not conducive to reducing the EOT size of the input / output MOS device, because the usual way to reduce the EOT size is to reduce the physical thickness of the gate dielectric layer, but doing so will cause leakage of the gate dielectric layer and electrical reliability The performance is reduced, which in turn leads to the reduction of the electrical performance of the input / output MOS device.

[0048] Therefore, the present invention provides a method for forming a gate structure, comprising the following steps:

[0049] providing a substrate, the substrate including a first region for forming an input / output MOS device and a second region for forming...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com