Semiconductor device

A semiconductor and device technology, applied in the field of semiconductor devices, can solve the problems of reduced solder welding area, difficulty in ensuring installation strength, and reduction in installation strength, and achieve the effect of realizing the installation area and ensuring the installation strength

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

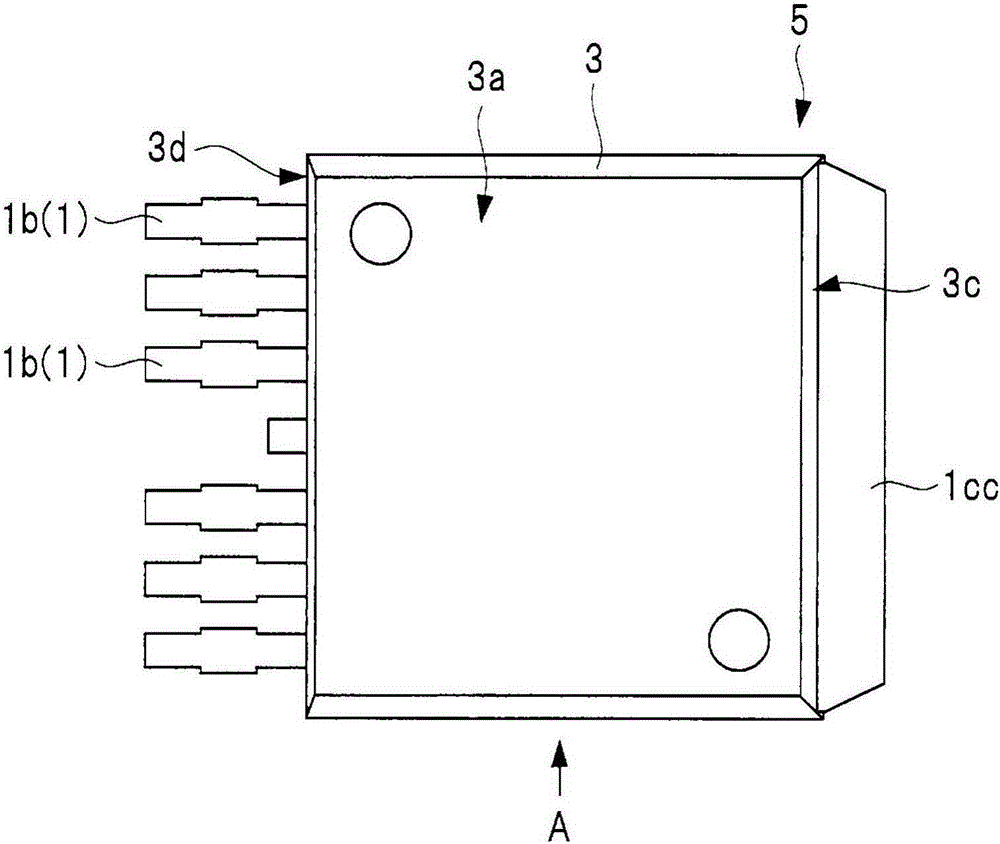

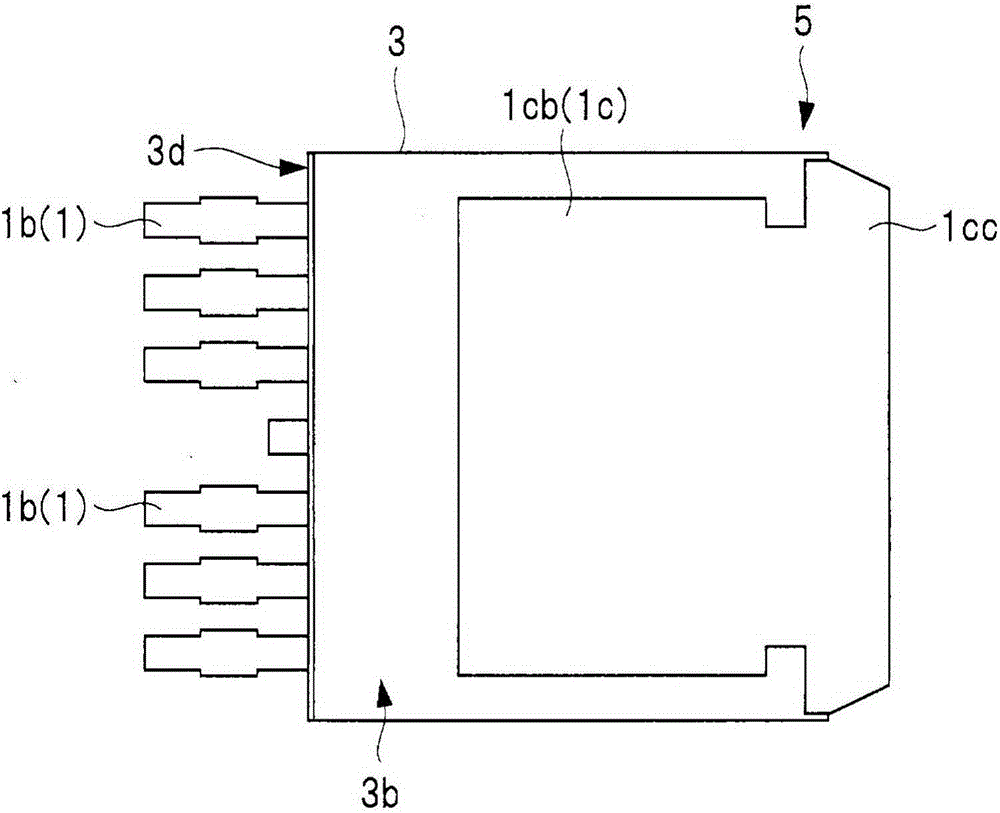

[0077] figure 1 It is a plan view showing an example of the structure of the semiconductor device of the embodiment, figure 2 From figure 1 The view from the direction A shown, image 3 yes means figure 1 A rear view showing an example of the structure of the back side of the semiconductor device, Figure 4 is expressed in perspective figure 1 A perspective top view of the configuration of the interior of the semiconductor device is shown. in addition, Figure 5 is along Figure 4 A cross-sectional view of an example of the structure cut off by the A-A line, Image 6 is along Figure 4 A cross-sectional view and a partially enlarged cross-sectional view of an example of a structure cut along the B-B line of .

[0078]

[0079] Figure 1 to Figure 6 The shown semiconductor device of this embodiment is a semiconductor package including a sealing body 3 that seals a semiconductor chip (also called a pellet) 2 and is formed of an insulating resin, and further has a 3...

Deformed example 1

[0229] In the above embodiments, the structure in which the plurality of outer lead portions 1b protrude from the side surface of the sealing body 3 of the semiconductor device has been described, but the semiconductor device may be, for example, Figure 31 and Figure 32 QFP20 shown.

[0230] here, Figure 31 is a plan view showing the structure of a semiconductor device according to a modified example of the embodiment, Figure 32 is along Figure 31 Cross-sectional view of the construct truncated by line A-A.

[0231] That is, the semiconductor device of this embodiment may also be Figure 31 and Figure 32 shown in the QFP20, at this time, with Figure 7 The shape of the outer lead portion 1b shown is similar, and the distance (length) L2 between the third intersection portion 1h and the fourth intersection portion 1i of the outer lead portion 1b is formed to be larger than that of the first intersection portion 1f of the outer lead portion 1b. The distance (length)...

Deformed example 2

[0234] The solder for the plating film formed in the external plating process of the above-mentioned embodiment, or the solder 9 which is an example of the die-bonding material 6, or the solder 9 used for solder bonding at the time of semiconductor device mounting does not substantially contain lead (Pb). The case of lead-free solder was described, but the above-mentioned solder may be lead-containing solder. However, in consideration of environmental pollution, it is preferable to use a solder formed of the above-mentioned lead-free solder.

[0235] Here, the lead-free solder refers to a solder with a lead (Pb) content of 0.1 wt % or less, which is determined in accordance with the RoHS (Restriction of Hazardous Substances: Restriction of the Use of Certain Hazardous Substances in Electrical and Electronic Equipment) directive.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com