On-chip reset system and reset method of SoC

A system-on-chip and chip technology, which is applied to the on-chip reset system and reset field of the system-on-chip, can solve problems such as incorrect chip working status and unstable chip working status, so as to improve register scalability and meet the start-up time Requirements, cost reduction effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

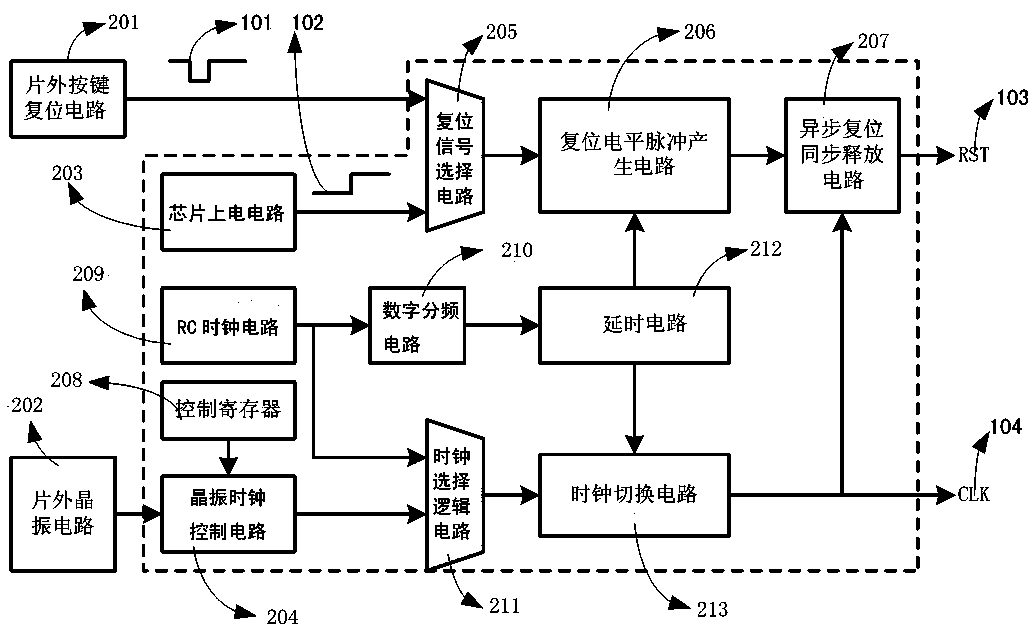

[0031] attached figure 1 It is a schematic diagram of the on-chip reset system of the system-on-chip chip of the present invention. In the figure, 101 is a button reset signal, 102 is a power-on reset signal, 103 is a reset signal, 104 is a SOC chip main frequency clock signal, and 201 is an off-chip button reset circuit, 202 is an off-chip crystal oscillator circuit, 203 is a chip power-on circuit, 204 is a crystal oscillator clock control circuit, 205 is a reset signal selection circuit, 206 is a reset level pulse generation circuit, 207 is an asynchronous reset synchronous release circuit, and 208 is a control circuit Register, 209 is an RC clock circuit, 210 is a digital frequency division circuit, 211 is a clock selection logic circuit, 212 is a delay circuit, and 213 is a clock switching circuit. As can be seen from the figure, the on-chip reset system of the SoC chip of the present invention includes an off-chip button reset circuit 201, an off-chip crystal oscillator c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com