A method for preventing excessive etching of ICP in a sog-mems chip

An over-etching and chip technology, which is applied in the fields of crafts, decorative arts, and gaseous chemical plating for producing decorative surface effects, to achieve the effects of improving yield, reducing costs, and preventing over-etching

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

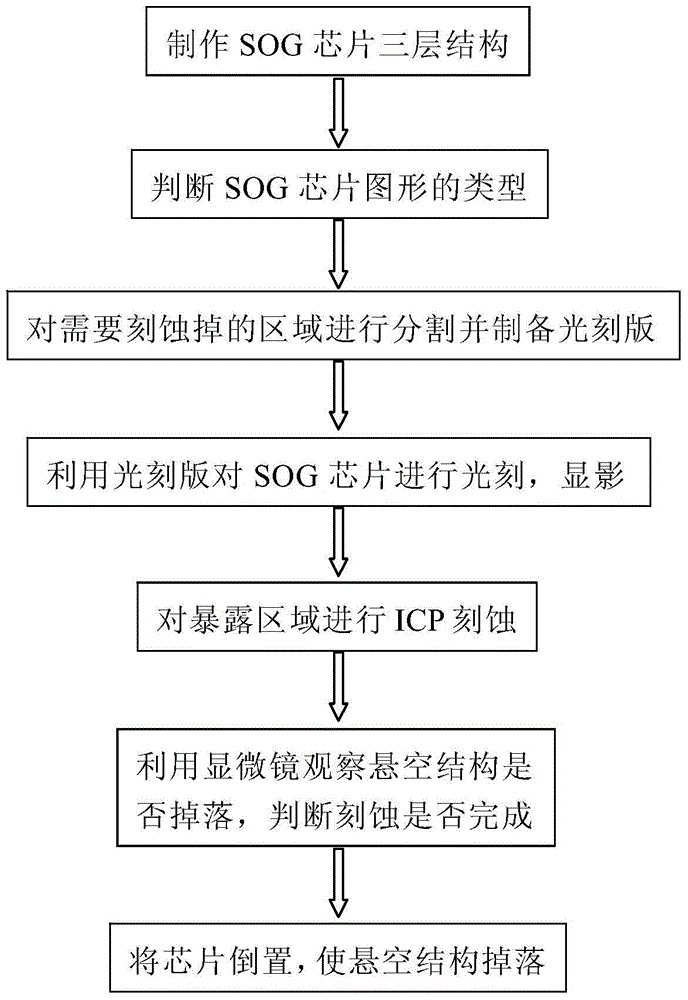

[0033] Embodiment 1: The pattern processing includes etching away a plurality of rectangles and etching through a plurality of linear chips composed of the same line width. Processing flow such as figure 1 shown.

[0034] 1. Preparation of SOG chip.

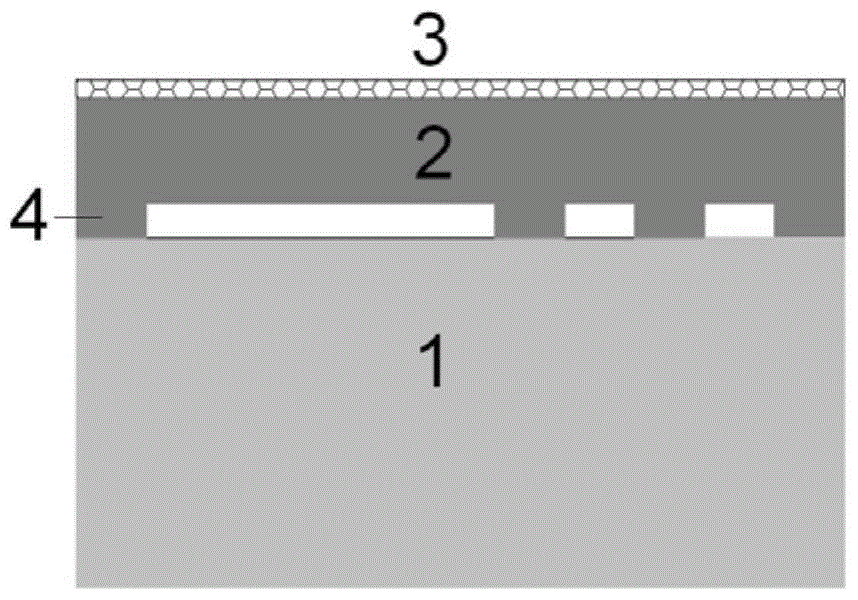

[0035] SOG structure such as figure 2 As shown, it includes a support layer 1, a structure layer 2, and a mask layer 3; the support layer 1 is made of glass material, the structure layer 2 is made of silicon material, and the mask layer 3 is made of photoresist. A plurality of anchor points 4 are etched on the side of the silicon layer facing the glass layer. The height of the anchor points is generally 5-30um. In this example, the height of the anchor points is set to 10um. An isolation groove 5 is formed between every two anchor points 4 The silicon wafer is connected with the glass wafer through the anchor point; the glass layer and the silicon layer are bonded together and the silicon layer is thinned by chemical mechanic...

Embodiment 2

[0058] Embodiment 2: The pattern processing includes etching out multiple rectangles and etching through multiple linear chips composed of different line widths.

[0059] Processing flow such as figure 1 shown.

[0060] 1, the preparation of SOG chip is the same as embodiment one;

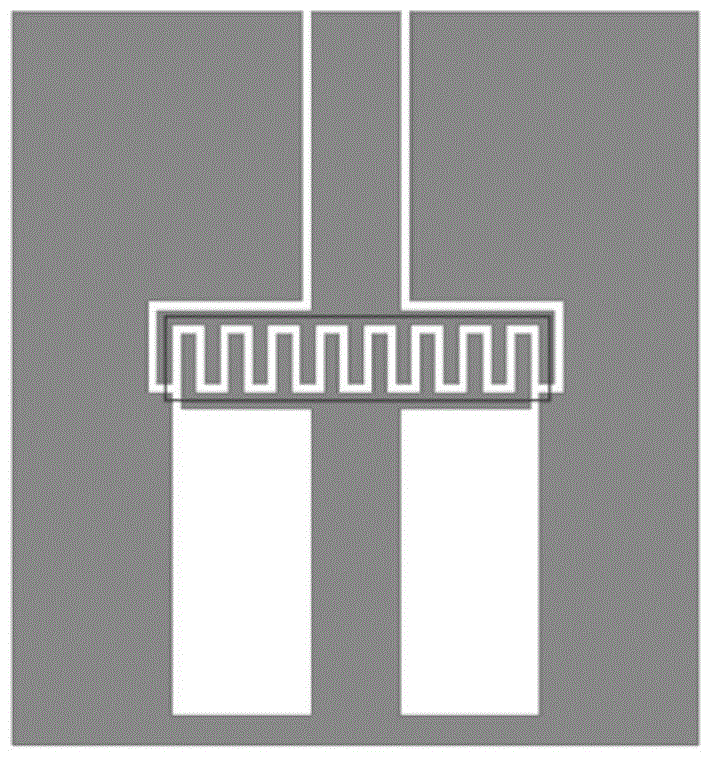

[0061] 2. Determine the type of chip graphics.

[0062] The pattern of the chip also includes etching away 4 rectangles and etching through 16 lines with different line widths. The schematic diagram of the surface structure is shown in Figure 4(a). The white rectangular area in the figure is the etched area. The minimum side length of the rectangle is 45um. The area in the wire frame is a line shape composed of different line widths. The line width in area a is the smallest, which is 3um, and the line width in area b is The line width in area b is 5um, the line width in area c is 5um, and the line width in area d is the largest, which is 6um. The length of the shortest side of the rectangle is ...

Embodiment 3

[0071] Embodiment three: processing chips of other linear structures

[0072] The linear structure can be H-shaped or other shapes, and the end of the linear structure can be rectangular or arc-shaped. These structures are widely used in MEMS devices.

[0073] All the other steps are the same as in Embodiment 1.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com