FinFET manufacturing method

A manufacturing method and fin technology, which are applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems affecting the threshold voltage and sub-threshold characteristics of the device, and achieve the purpose of suppressing the diffusion of impurities, optimizing the process, and improving the device. performance effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] In view of the above problems, the present invention provides a FinFET manufacturing method, which enables PTSL to be effectively distributed in the region where the punch-through current occurs without introducing impurity distribution into the channel. Specifically, the method includes:

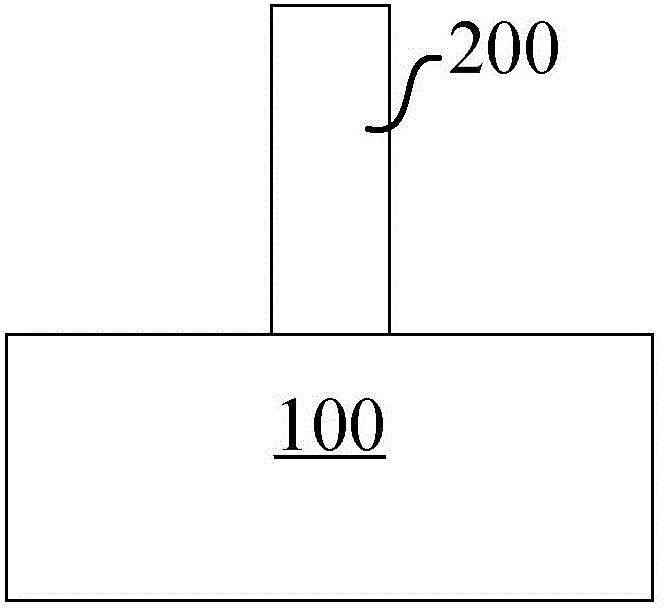

[0021] a. providing a substrate 100, and forming fins 200 on the substrate;

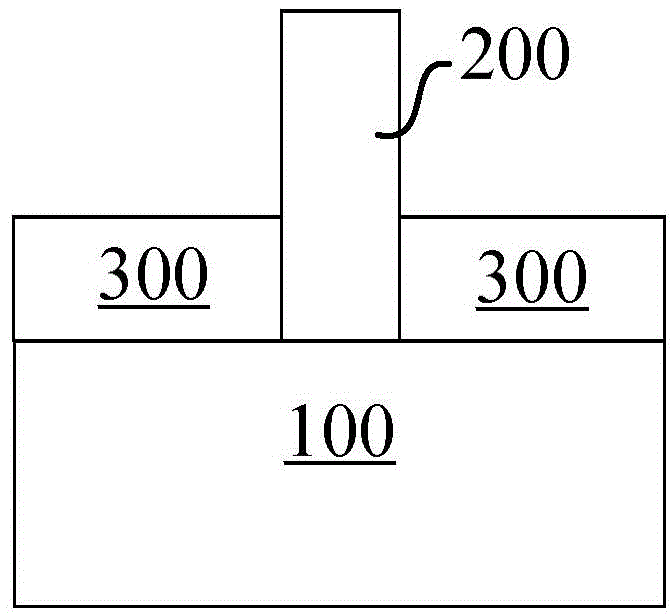

[0022] b. forming isolation layers 300 on the substrates on both sides of the fin 200;

[0023] c. forming a punch-through barrier layer 310 and a diffusion barrier layer 320 in the fins on both sides of the upper half of the isolation layer 300;

[0024] d. Forming source and drain regions at both ends of the fin, forming a gate structure in the middle of the fin, and filling an interlayer dielectric layer 500 above the isolation layer 300 . Wherein, the penetration barrier layer 310 and the diffusion barrier layer 320 are formed by lateral scattering of impurity particles from the isolation layer 300 in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com