A High Speed Low Power Dynamic Comparator

A dynamic comparator, low power consumption technology, applied in the direction of reducing power consumption, reducing power of field effect transistors, improving reliability, etc., can solve problems such as speed, power consumption and low power supply voltage that are difficult to meet at the same time. Static power consumption, high speed and power consumption, the effect of simple structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The preferred embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings; it should be understood that the preferred embodiments are only for illustrating the present invention, rather than limiting the protection scope of the present invention.

[0019] In order to understand the technical solution of the present invention in more detail, the working principles and advantages and disadvantages of several traditional structure comparators are firstly analyzed.

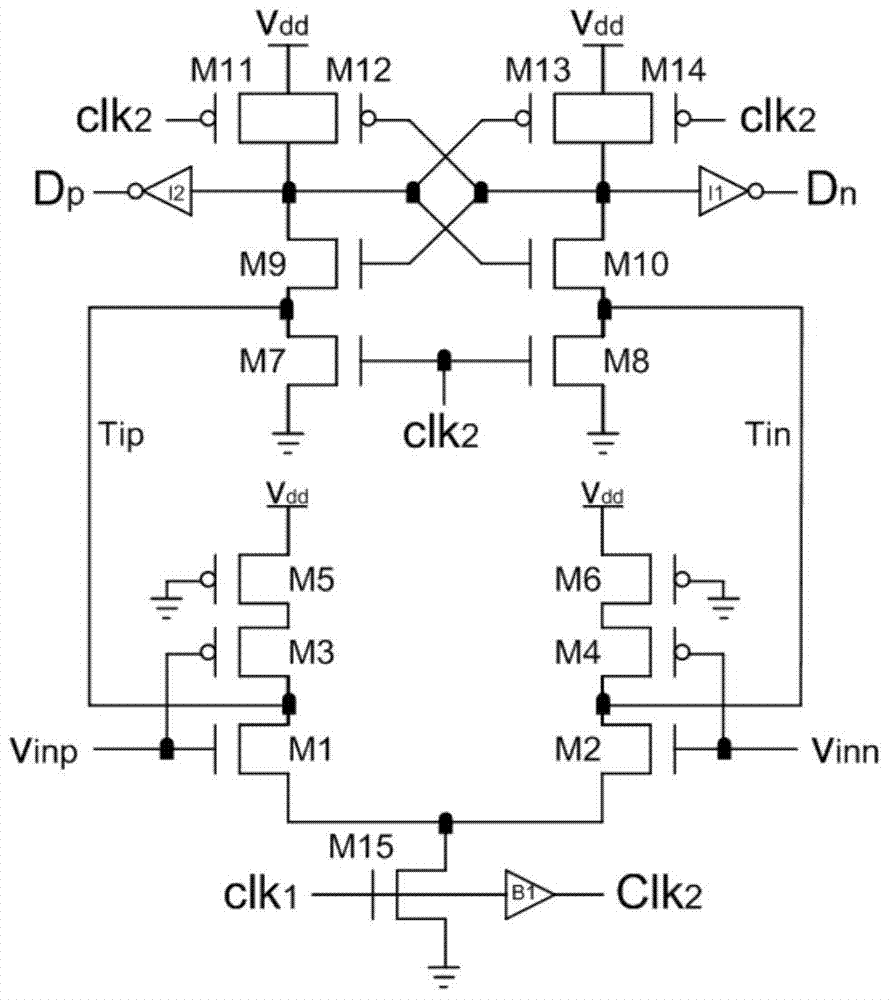

[0020] figure 1 It shows a schematic diagram of a high-speed low-offset dynamic comparator structure (referred to as the structure [1]), when the control signal clk1 is low, clk2 as the delay signal of clk1 is also low, and the NMOS transistors M7 / M8 / M15 In the off state, the PMOS transistor M11 / M14 is turned on, through the inverter I1 / I2, the comparator output signals Dp and Dn are low level, and the comparator is in the reset state; when clk1 / clk2 beco...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com