System level optimization method for power supply voltage of SOI process

A technology of power supply and optimization method, which is applied in the fields of electrical digital data processing, instruments, calculations, etc., can solve problems such as circuit performance weakening, and achieve the effect of maximizing circuit performance and minimizing circuit power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The technical solution of the present invention will be further described below in conjunction with the drawings and specific embodiments.

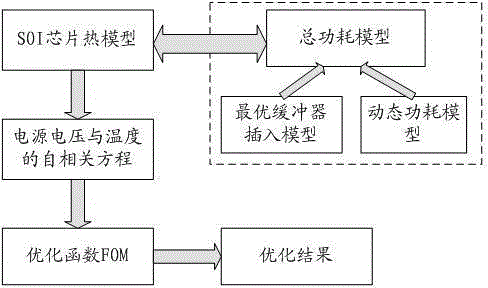

[0030] figure 1 This is a flowchart of a system-level optimization method for SOI process-oriented power supply voltage proposed by an embodiment of the present invention. With reference to the figure, the specific steps of the embodiment of the present invention are as follows:

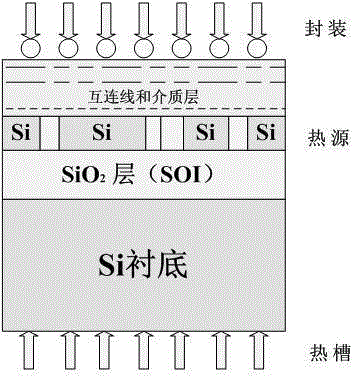

[0031] (1) Establish as figure 2 Thermal model of the chip shown:

[0032]

[0033] It can be estimated from the substrate temperature and total power consumption of a specific chip in the same package.

[0034] for ,among them Is the thickness of the buried oxide layer, Is the thermal conductivity of the buried oxide layer, and A is the area where the transistor generates power.

[0035] (2) Definition

[0036] (3) Definition with Analytical model

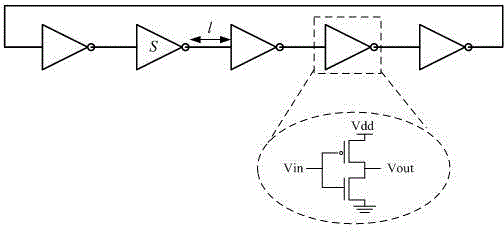

[0037] (4) Different with SPICE with Under the bias conditions, simulate a image 3 The time delay of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com