A wafer level chip packaging method

A technology of wafer-level chip and packaging method, which is applied in the direction of semiconductor devices, electrical components, circuits, etc., and can solve problems such as surface mount process difficulties, chip edge chipping, and missing corners

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

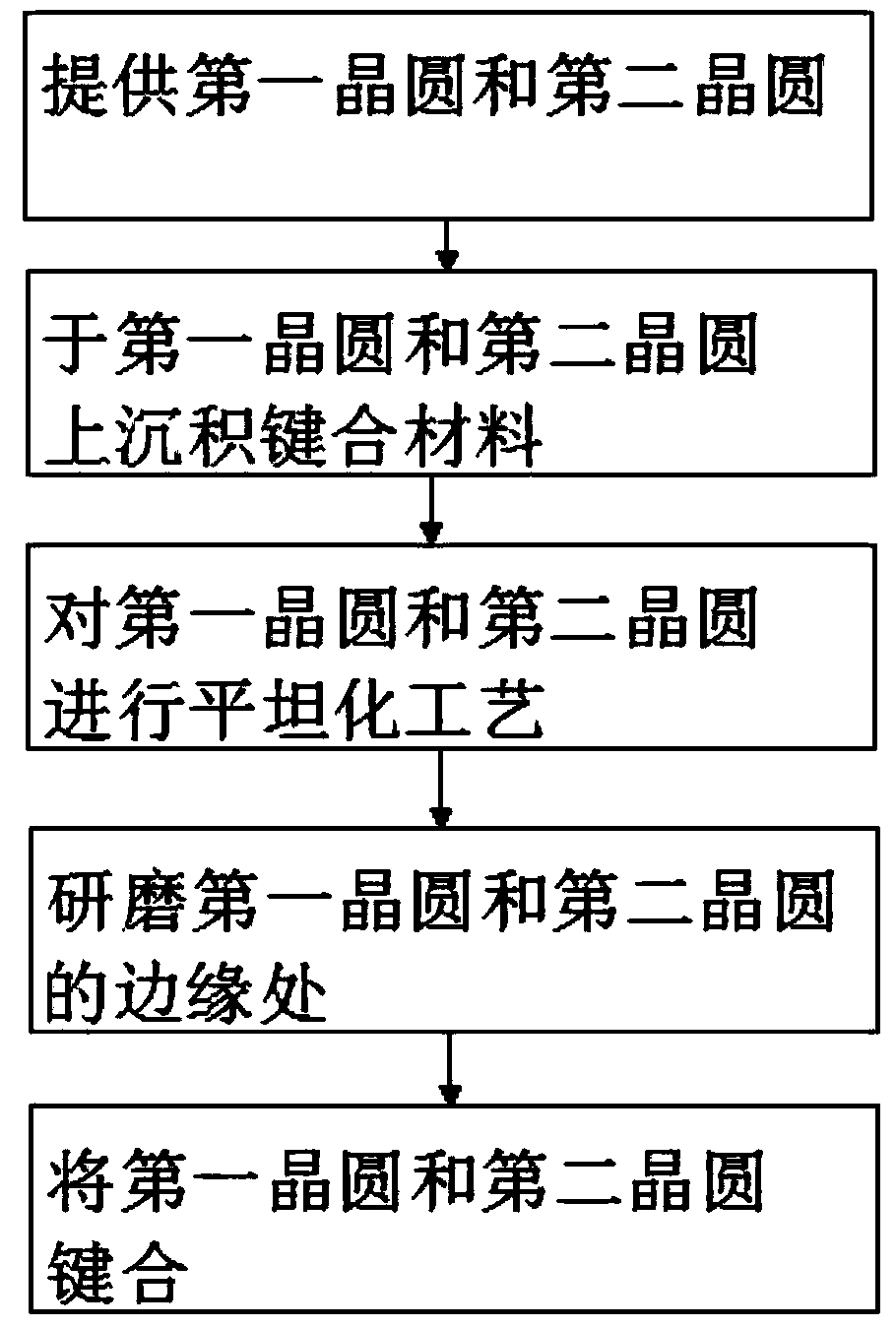

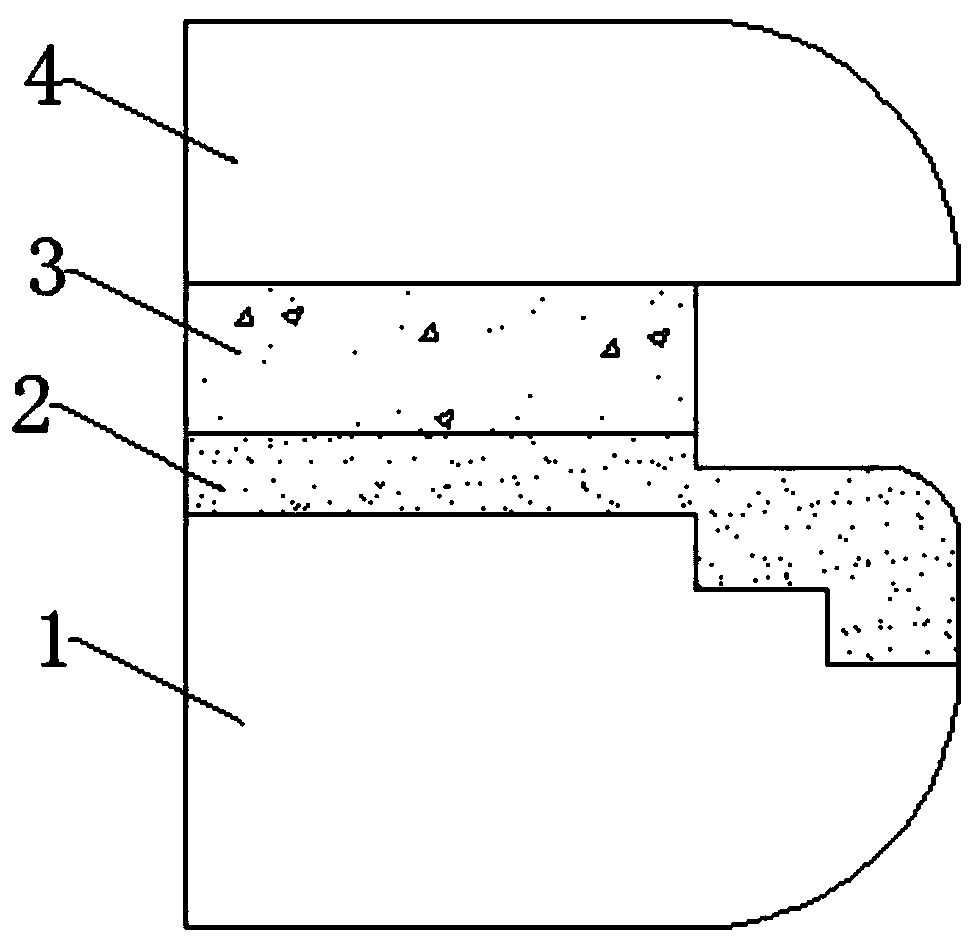

[0021] In order to make the technical solutions and advantages of the present invention more comprehensible, further details will be described below in conjunction with the accompanying drawings. It should be noted that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0022] The biggest feature of the wafer-level chip packaging method is that its package size is small, the inductance between the IC and the PCB is small, and the production cycle is shortened, so it can be used in portable products and meets the requirements of light, thin, and small. Information The transmission path is short, the stability is high, and the heat dissipation is good.

[0023] Since the wafer-level chip package lacks the traditional sealed plastic or ceramic package, the heat of the IC chip can be effectively dissipated during operation without increasing the temperature of the host. This feature has many benefits for th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com