Multilevel fault tolerance reinforcement satellite information processing system based on SRAM FPGA

An information processing system and satellite technology, applied in the field of satellite information processing, can solve problems such as affecting system reliability, and achieve the effect of improving reliability and performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

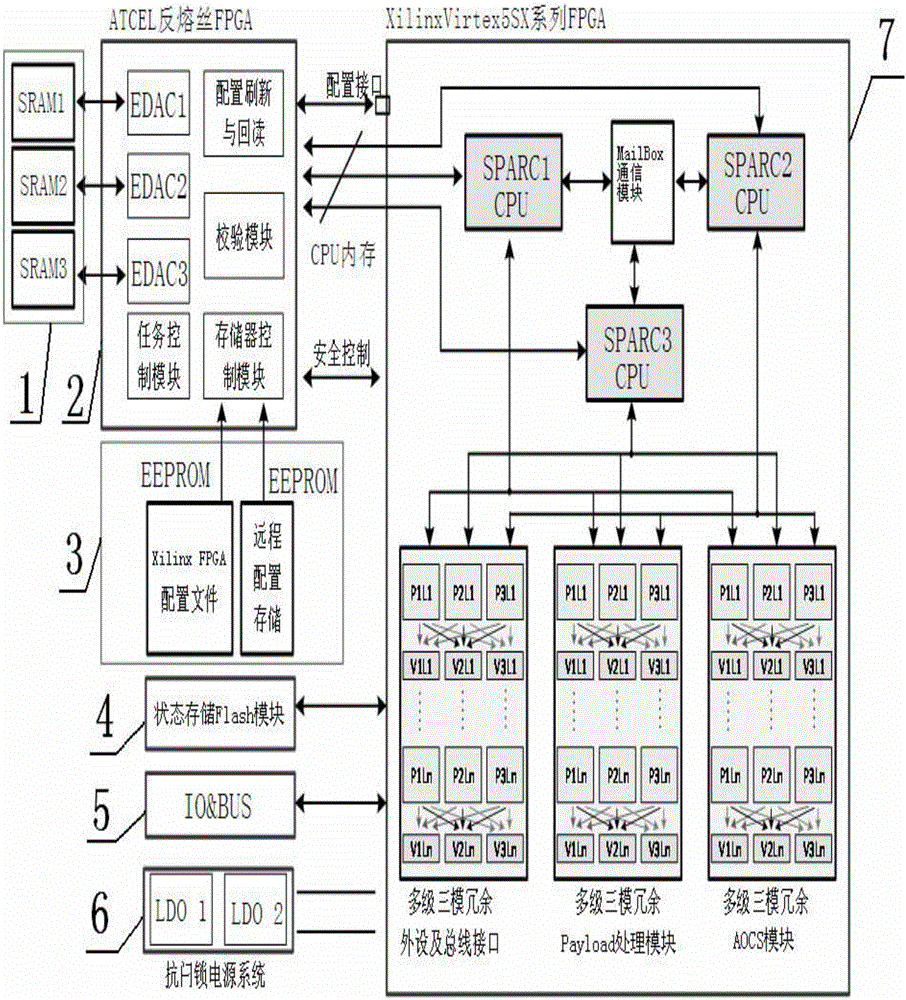

[0023] Specific implementation mode one: the following combination figure 1Illustrate this embodiment, a kind of multilevel fault-tolerant reinforcement satellite information processing system based on SRAMFPGA, it comprises:

[0024] The value range of multiple in multi-level is greater than or equal to 2;

[0025] Aiming at the SRAMFPGA process characteristics, harsh working environment in space, processing performance and reliability requirements, and considering the actual on-orbit mission requirements, design the XilinxFPGA-based Virtex-5SX series FPGA onboard data processing unit solution, which is the core unit of the onboard computer , designing a small amount of devices such as the communication interface required by the extended task of the unit can be used as an on-board computer; the unit can realize the processing tasks of C&DH, AOCS, Payload and other functions. The structure of the unit is as follows: figure 1 As shown; SRAM is static random access memory, EDAC...

specific Embodiment approach 2

[0040] Specific Embodiment 2: This embodiment further explains Embodiment 1. The verification and control module of single event effect immunity described in this embodiment includes:

[0041] The EDAC verification module is used to encode, decode, verify and correct the data in the memory, provide highly reliable storage for the LEON3 processor of the main processing module, and ensure the correct execution of the program;

[0042] EDAC verification module, the anti-fuse FPGA is connected to three external SRAMs (memory modules), and corrects and controls errors through the internal EDAC, so as to provide highly reliable memory for the LEON3 processor inside the main processing module . By using the EDAC mechanism based on Hamming coding inside the antifuse FPGA (single event effect immune verification and control module), the data verification and correction of the memory is realized, and the LEON3 processor of the main processing module provides a highly reliable external ...

specific Embodiment approach 3

[0053] Specific implementation mode three: this implementation mode further explains implementation mode one, and the main processing module described in this implementation mode includes:

[0054] The LEON3 processor IP core module is used to complete star management, task control, and internal communication and control with the main processing module;

[0055] LEON3 processor IP core: Inside the FPGA, use its logic resources to realize three LEON3 processor IP cores, and perform triple-mode redundant backup to improve reliability. A single LEON3 processor requires 4,000 LUTs, and Virtex5SX series FPGAs can have up to 149,760 LUTs, which fully meets the application requirements of simultaneously implementing three LEON3 processors;

[0056] The LEON3 processor is based on the SPARCV8 soft-core processor architecture, which itself has a multi-layer fault-tolerant mechanism to provide highly reliable computing services; the MailBox module is used to communicate among the three ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com