A test structure and its manufacturing method

A technology for testing structures and manufacturing methods, applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve problems such as easy damage and unfavorable failure analysis, so as to avoid device damage, improve failure analysis efficiency, and reduce cost effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

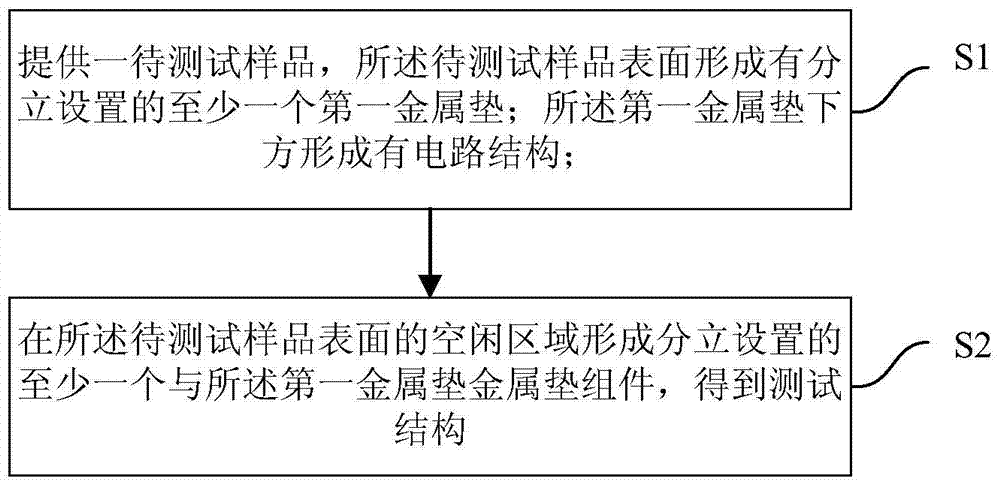

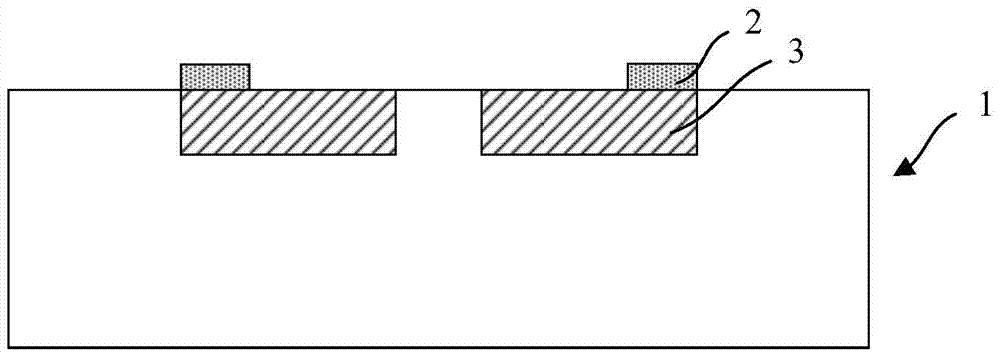

[0046] see Figure 2 to Figure 5 , is shown as an embodiment of the manufacturing method of the test structure of the present invention.

[0047] See first figure 2 , performing step S1: providing a sample to be tested 1, the surface of the sample to be tested 1 is formed with at least one discrete first metal pad 2; a circuit structure 3 is formed under the first metal pad 2.

[0048] Specifically, the sample 1 to be tested can be a device structure that has passed a reliability test. After the reliability test, failure analysis needs to be performed, and the chip can be unpacked to take out the device structure. During the removal process, the device structure has been bonded before. The bonded wires are pulled off, and because electrical signals need to be connected in failure analysis, it is necessary to re-bond the wires (also called wire bonding).

[0049] Specifically, the first metal pad 2 may be a metal pad such as an aluminum pad or a copper pad. Due to the minia...

Embodiment 2

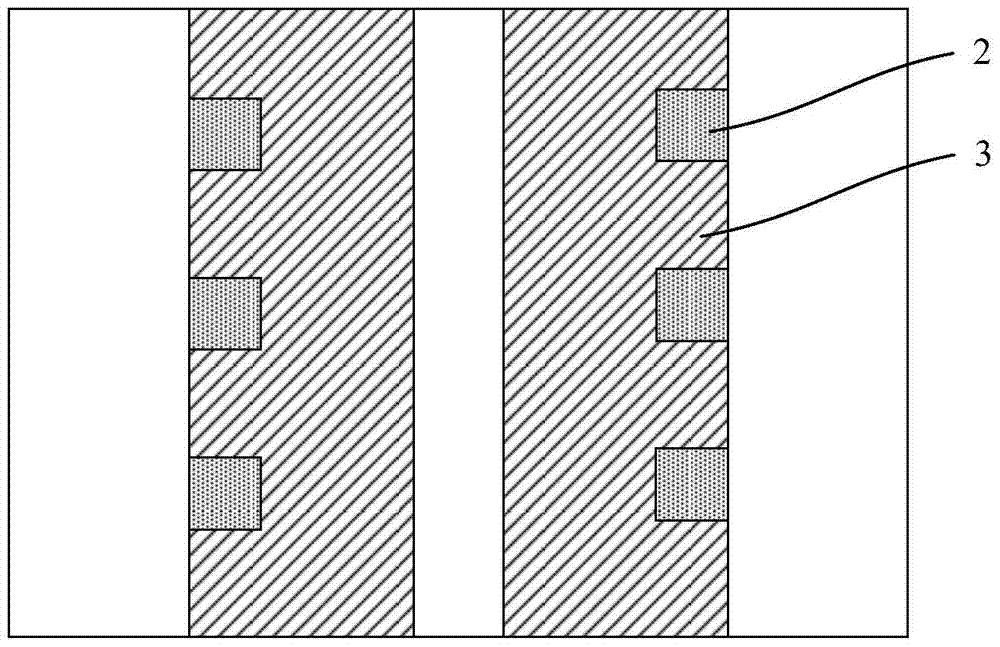

[0058] see Figure 6 to Figure 7 , showing another embodiment of the manufacturing method of the test structure of the present invention.

[0059] See first Figure 6 , performing steps S1 and S2: providing a sample to be tested, the surface of the sample to be tested is formed with at least one discrete first metal pad 2; a circuit structure 3 is formed under the first metal pad 2; The free area on the surface of the sample to be tested forms at least one discrete metal pad assembly connected to the first metal pad 2 to obtain a test structure.

[0060] Specifically, the metal pad assembly is composed of a pair of second metal pads 4, the pair of second metal pads are connected to each other by a metal wire 5, and one of the second metal pads is connected to the first metal pad. In this embodiment, the sample to be tested is described as an example including two columns of circuit structures 3 and corresponding two columns of first metal pads 2 . The metal pad assembly is ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com