Low-power-consumption readout circuit based on folding comparator and control method

A technology for reading circuits and comparators, applied in instruments, static memory, digital memory information, etc., to achieve the effects of small hardware consumption, increased output swing and gain, and improved reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The technical solution of the present invention will be specifically described below in conjunction with the accompanying drawings.

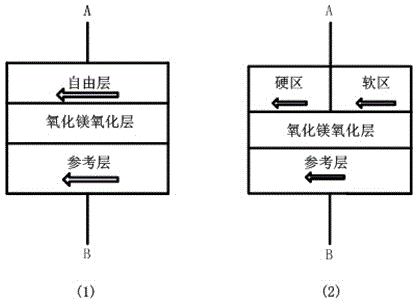

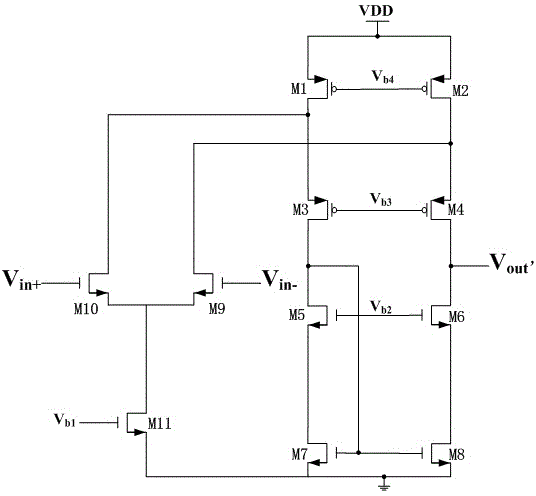

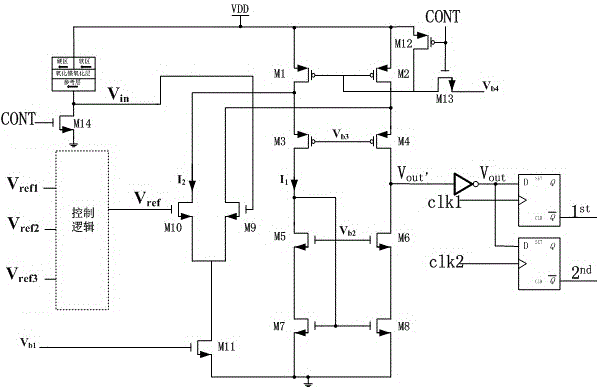

[0027] Such as Figure 1-7As shown, the present invention is a low-power reading circuit based on a folding comparator, including a folding cascode comparator and a control circuit connected to the folding cascode comparator, a parallel magnetic tunnel junction, A control logic circuit and an inverter, the control circuit is connected to the parallel magnetic tunnel junction, the inverter is also connected to a first D flip-flop and a second D flip-flop, and also includes a clock output module, the The first clock signal output end and the second clock signal output end of the clock output module are respectively connected to the clock control input ends of the first D flip-flop and the second D flip-flop; the folded cascode comparator includes The first to eleventh MOS transistors, the source of the first MOS transistor and the source o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com