Low-temperature polycrystalline silicon TFT substrate structure and manufacturing method thereof

A technology of low-temperature polysilicon and manufacturing methods, which is applied in the direction of transistors, semiconductor/solid-state device manufacturing, electrical components, etc., and can solve the problems of uneven distribution, lattice uniformity, and lattice crystallization direction that cannot be effectively controlled, and long-term display effects. Uniformity and other issues, to achieve the effect of improving uniformity, improving electron mobility, and ensuring uniformity of grain boundaries

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0052] In order to further illustrate the technical means adopted by the present invention and its effects, the following describes in detail in conjunction with preferred embodiments of the present invention and accompanying drawings.

[0053] see Figure 5 , the present invention at first provides a kind of fabrication method of low-temperature polysilicon TFT substrate structure, comprises the following steps:

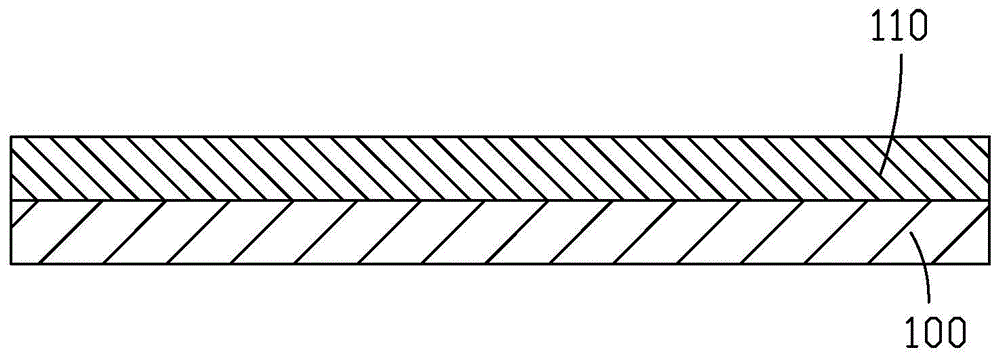

[0054] Step 1, such as Image 6 As shown, a substrate 1 is provided, the substrate 1 includes a driving TFT region and a display TFT region, and a buffer layer 11 is deposited on the substrate 1 .

[0055] Specifically, the substrate 1 is a glass substrate, and the material of the buffer layer 11 may be silicon oxide (SiOx), silicon nitride (SiNx), or a combination of both.

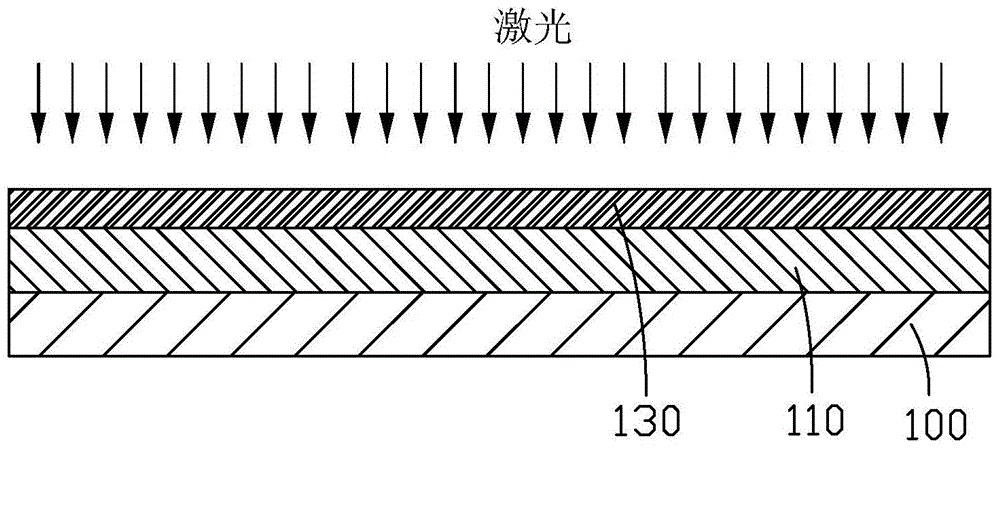

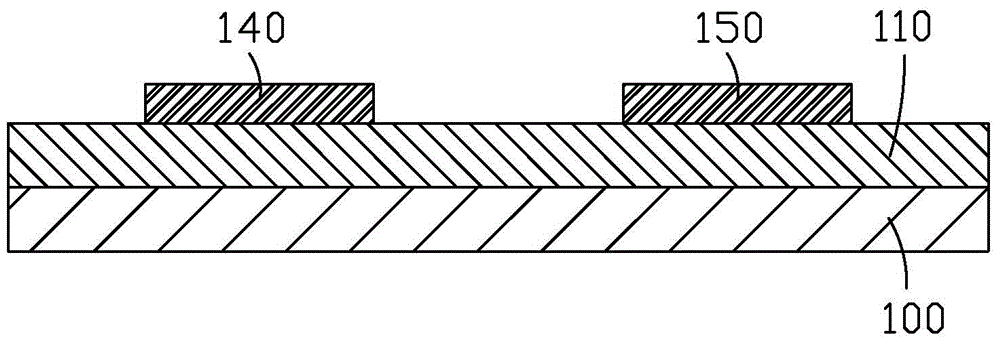

[0056] Step 2, such as Figure 7 As shown, an amorphous silicon layer 12 is deposited on the buffer layer 11, and the amorphous silicon layer 12 is patterned so that the thickness of the amo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com