Task scheduling optimizing method based on SMP (symmetric multi-processing) system

A technology of task scheduling and optimization method, applied in the direction of program startup/switching, resource allocation, multi-programming device, etc., can solve the problems of long-delay bottleneck of off-chip memory access operation, decrease of bus effective utilization, etc., to achieve easy promotion, Improve the overall utilization rate and the effect of strong practicability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

[0020] With the further increase in the speed gap between the processor and the main memory, the long-delay bottleneck of off-chip memory access operations will easily lead to a decrease in the overall effective utilization of the bus in the SMP system. The invention proposes an SMP system-based task scheduling optimization method, which mainly solves the problem of system bus resource utilization in the SMP multi-core and multi-thread scenario.

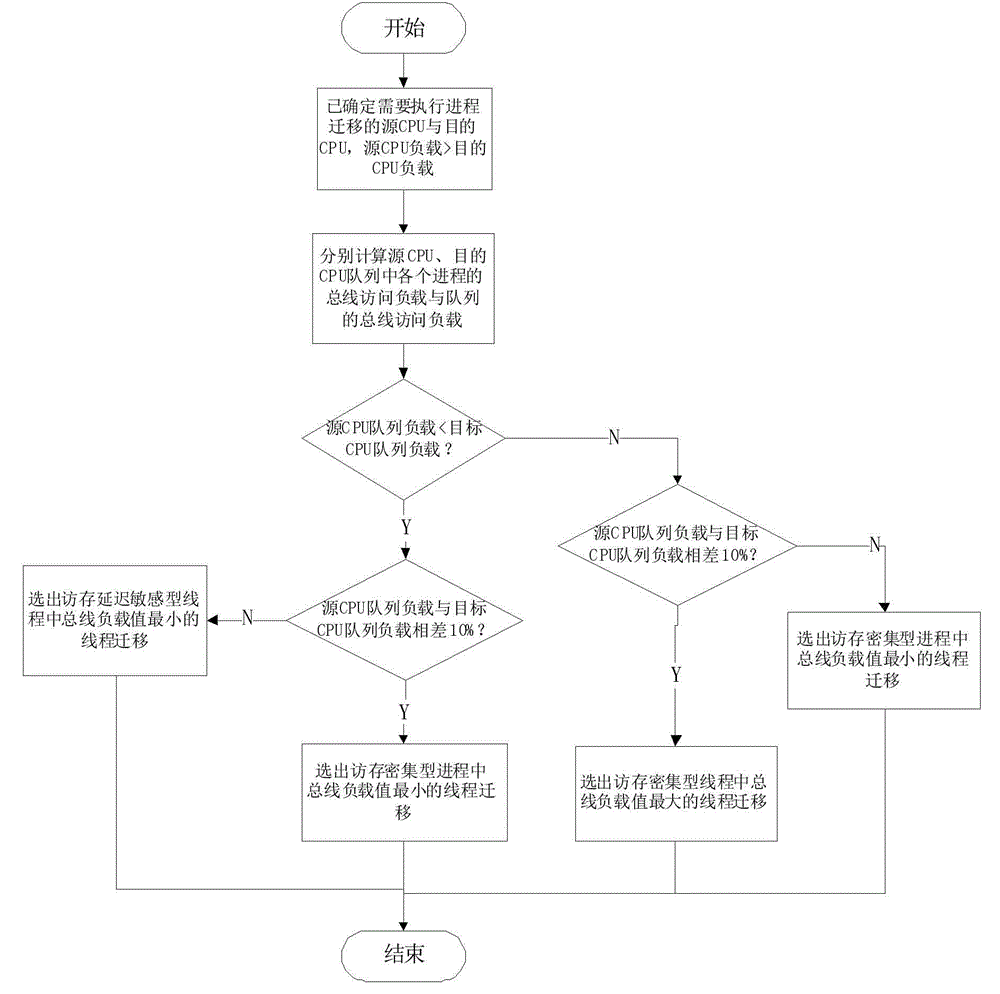

[0021] The purpose of the present invention is achieved in this way, adopting the scheduling idea based on the use of process bandwidth, if the process bandwidth usage that has been counted in advance can be considered when performing process migration, the SMP system bus bandwidth can be optimized while performing load balancing usage of.

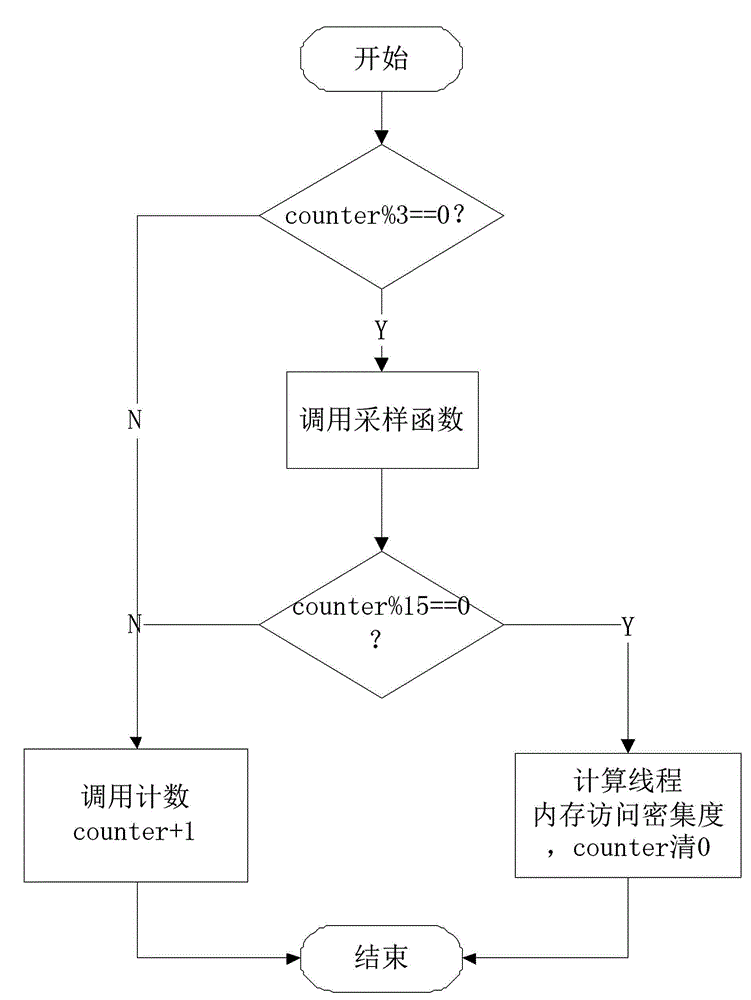

[0022] A task scheduling optimization method based on the S...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com