Single-converted-to-double low noise amplifier with highly balanced and stabilized differential output gain phase

A low-noise amplifier and differential output technology, applied in the direction of low-noise amplifiers, differential amplifiers, DC-coupled DC amplifiers, etc., can solve the problem of affecting the balance of the output differential signal, the absence of a high-impedance tail current source, and the balance of the output differential signal Poor problems, achieve good common-mode interference performance, improve common-mode rejection ability, and improve balance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The technical solution of the present invention will be further described in detail below in conjunction with the accompanying drawings, but the protection scope of the present invention is not limited to the following description.

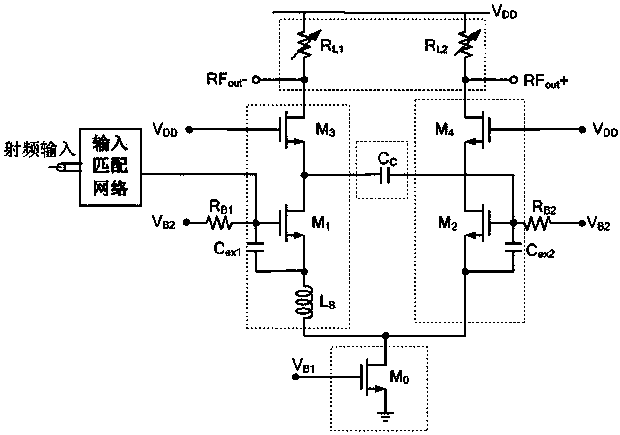

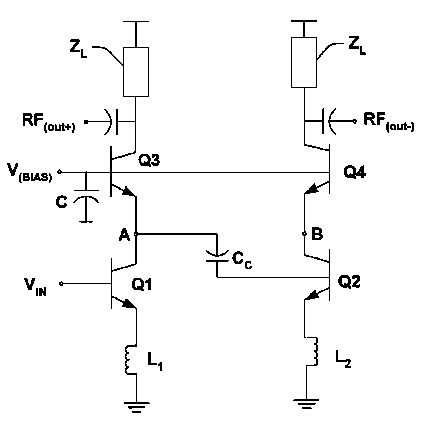

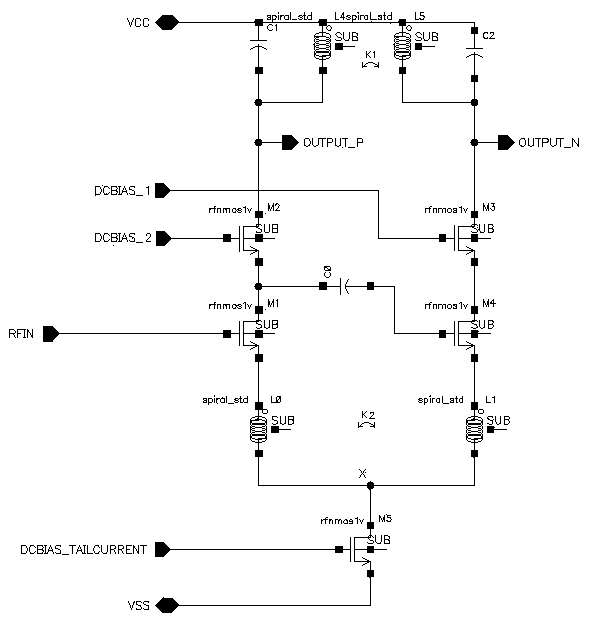

[0035] A highly balanced and robust differential output gain phase dual low-noise amplifier, which includes a common-source, common-emitter input amplifier transistor pair: the first transistor, the fourth transistor; common-gate, common-base amplifier transistor pair: the second transistor, a third transistor; a tail current source transistor and an output load circuit with a tightly coupled differential inductor.

[0036] The first transistor, the second transistor, the third transistor, the fourth transistor, and the tail current source transistor may all be field effect transistors, or all may be bipolar transistors.

[0037] Such as image 3 As shown, when the first transistor, the second transistor, the third transistor, the fourth t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com