DMOS device and manufacturing method thereof

A manufacturing method and device technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of chip conduction current difference and low cell integration, and achieve the goal of reducing distance and improving integration Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

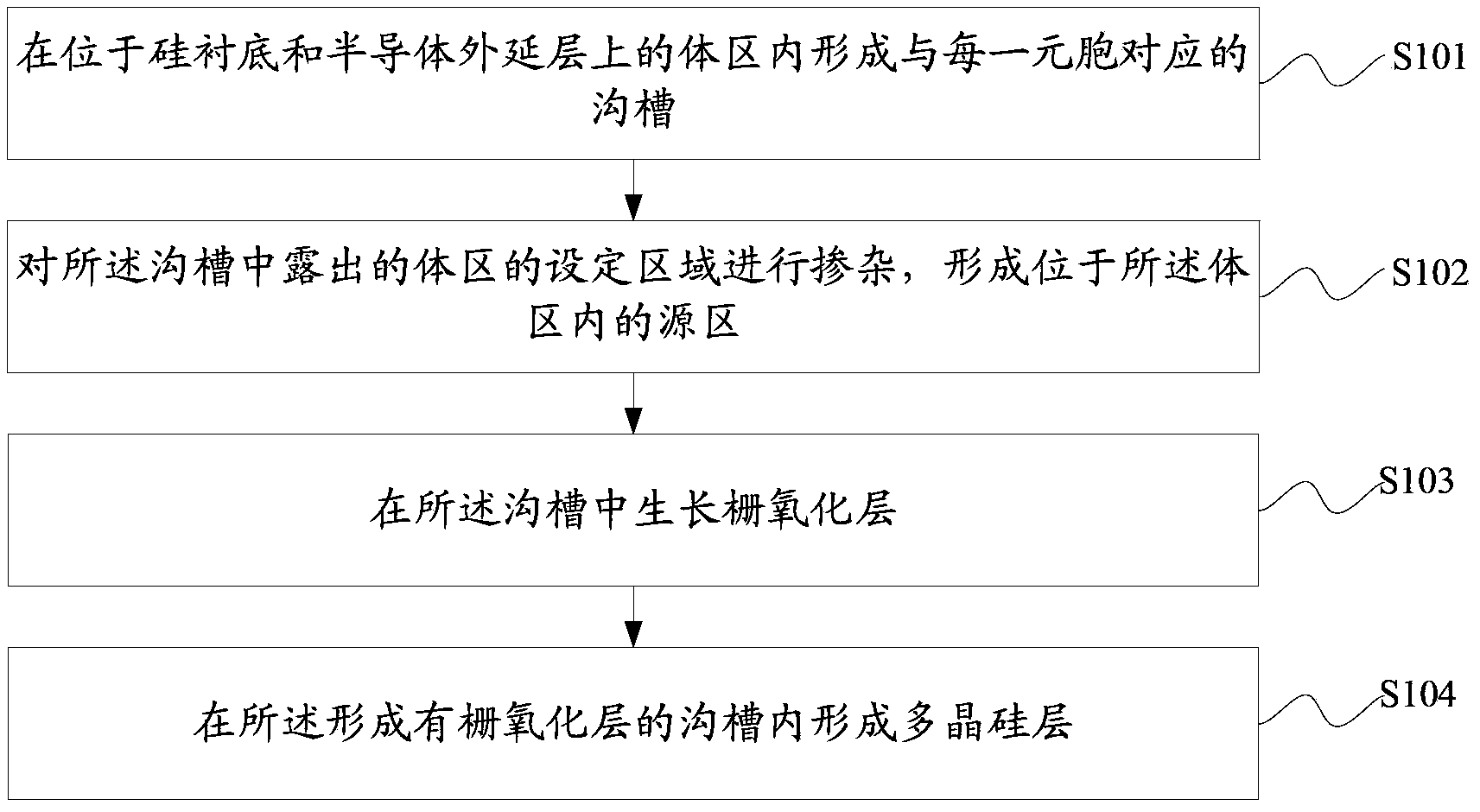

[0058] Embodiments of the present invention provide a DMOS device and a manufacturing method thereof, which are used to reduce the distance between adjacent cells on the DMOS device and improve the integration degree of the DMOS device.

[0059] The technical solutions provided by the embodiments of the present invention can be applied to the manufacture of trench-type DMOS devices.

[0060] In the method for fabricating a DMOS device provided by an embodiment of the present invention, a trench is first formed on the body region to expose the body region in the trench, and a set region in the exposed body region is doped to form a source region in the trench . The registration deviation caused by the existing photolithography process to form the source area is avoided, the distance between adjacent cells is reduced, and the integration degree of the DMOS device is improved.

[0061] The DMOS device provided by the embodiment of the present invention may include an N-type or P...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com