Back-to-back loopback validation method for large-scale interconnection chips based on detection logic addition

A technology of detection logic and verification method, which is applied in the field of back-to-back loopback verification based on added detection logic for large-scale interconnection chips, can solve problems such as the superposition of module uncertainty factors, and achieve the effect of fast processing speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

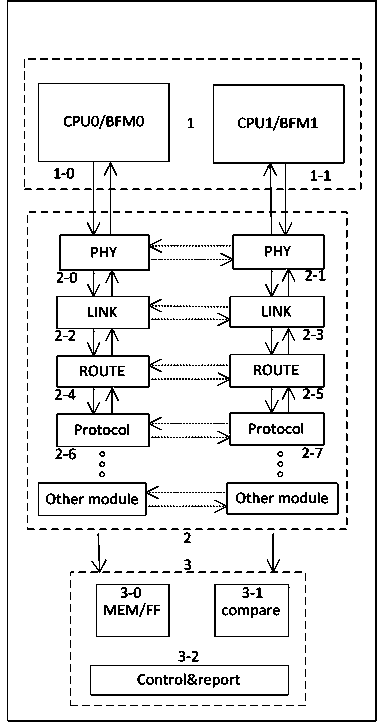

[0025] The purpose of the present invention is to provide a method for verifying simulation testing of large-scale interconnection chips and FPGA prototype verification by adding detection logic modules and back-to-back verification.

[0026] The realization of the present invention at first satisfies three prerequisites:

[0027] 1) The messages sent by each CPU / BFM (1-0, 1-1) can be divided into different types, and the number of unprocessed messages of the same type that can be sent must be within a certain range. First, avoid channel blockage. In addition, too much unprocessed message data will double the logic of the detection module (3), occupy too many logic resources and wiring resources in FPGA prototype verification, and make it difficult to meet the timing requirements of wiring.

[0028] 2) The time for each message to pass through the detected module must be less than a certain fixed value, which is determined through delay experiments, otherwise the detection m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com