Wafer-level chip packaging structure

A wafer-level chip and packaging structure technology, applied in radiation control devices and other directions, can solve the problems affecting the reliability and delamination of CIS products, and achieve the effects of high reliability, good chemical properties, and stress relief

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

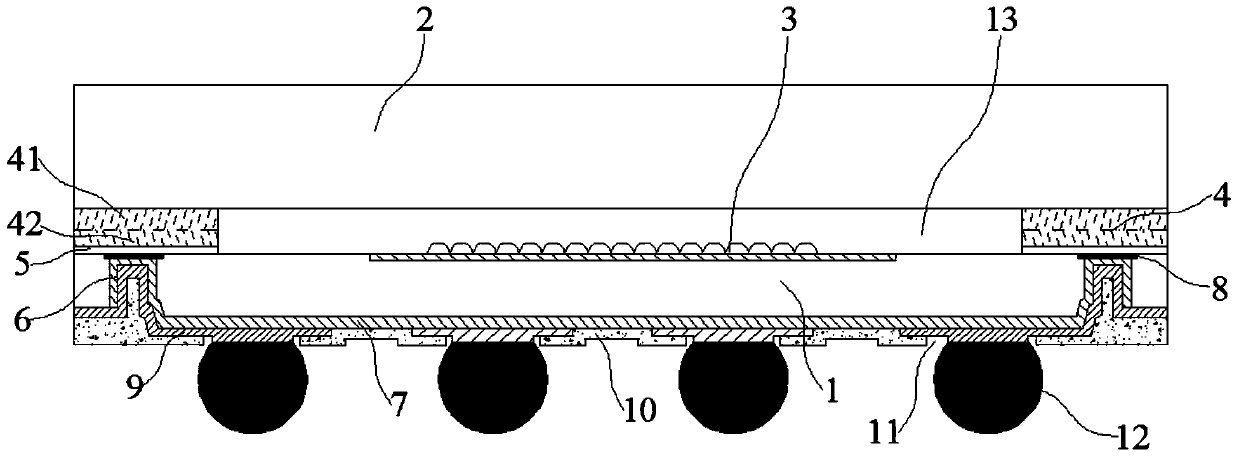

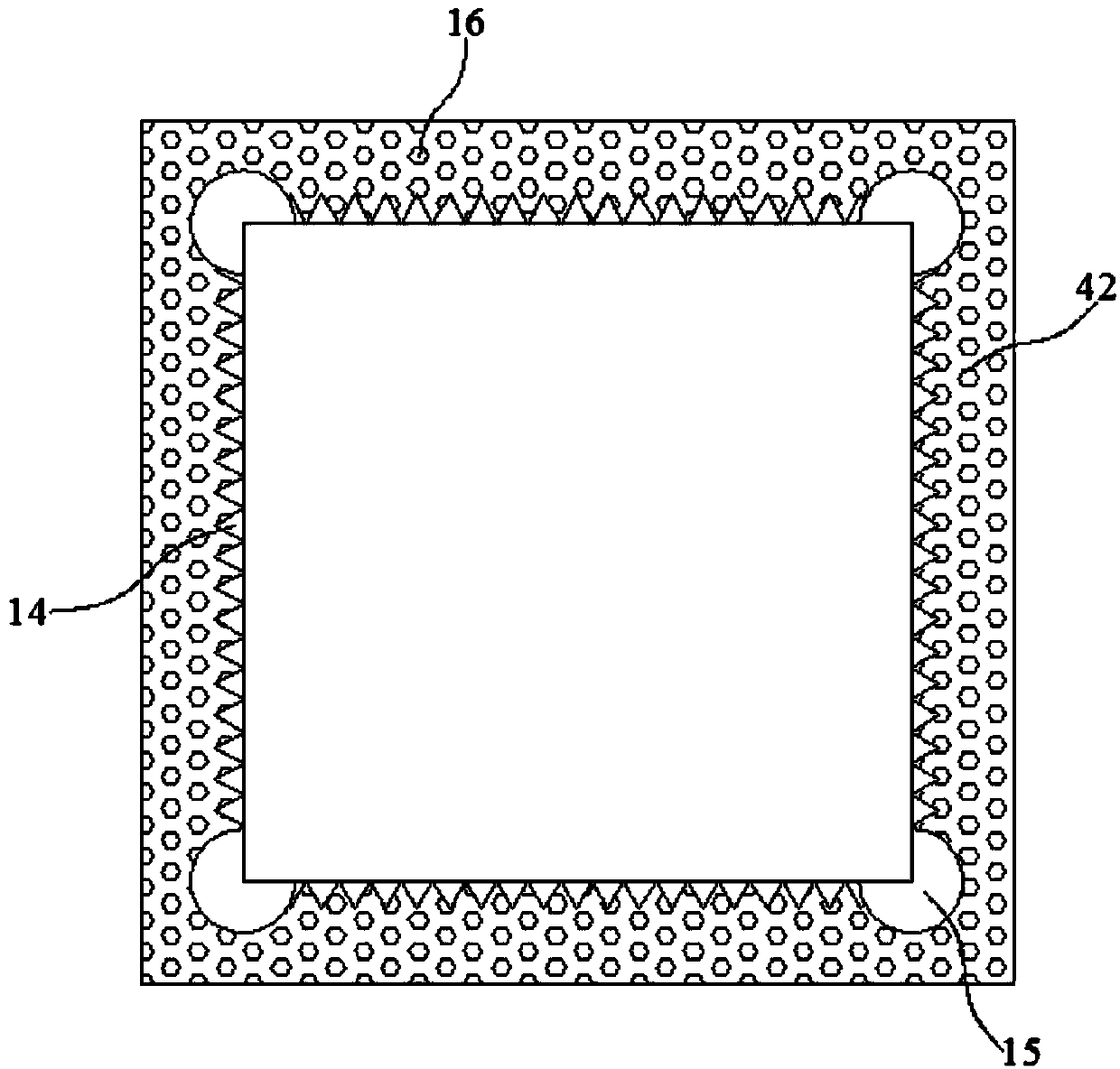

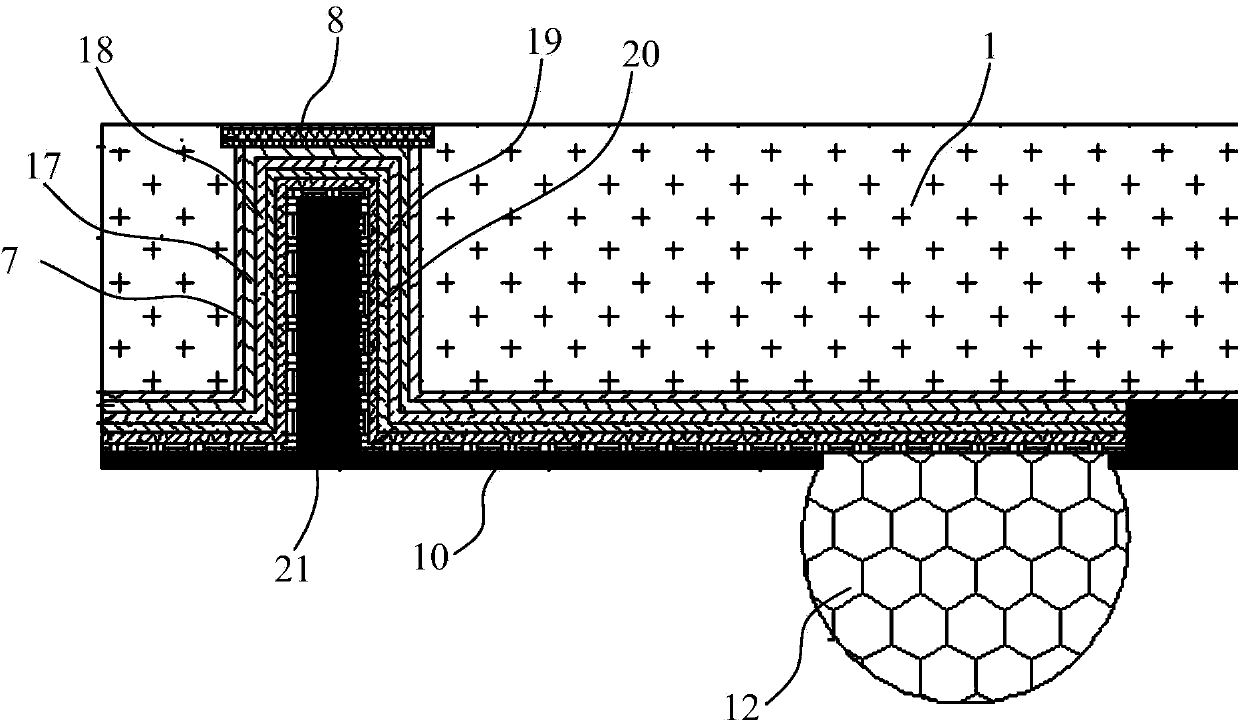

[0018] Embodiment 1: A wafer-level chip packaging structure, including an image sensor chip 1 and a transparent cover plate 2, the upper surface of the image sensor chip 1 has a photosensitive area 3, and the edge of the transparent cover plate 2 and the image sensor There is a support bank 4 between the upper surface edge of the chip 1 so as to form a cavity 13 between the transparent cover plate 2 and the image sensor chip 1, and the support bank 4 and the image sensor chip 1 are bonded by a glue layer 5 In combination, there are several blind holes 6 distributed around the edge area around the lower surface of the image sensor chip 1, the lower surface of the image sensor chip 1 and the side surfaces of the blind holes 6 have a passivation layer 7, and the bottom of the blind hole 6 has an image sensor The pin pad 8 of the sensor chip 1, the surface of the passivation layer 7 opposite to the image sensor chip 1 and the blind hole 6 have a metal conductive pattern layer 9 ele...

Embodiment 2

[0020] Embodiment 2: A wafer-level chip packaging structure, including an image sensor chip 1 and a transparent cover plate 2, the upper surface of the image sensor chip 1 has a photosensitive area 3, and the edge of the transparent cover plate 2 and the image sensor There is a support bank 4 between the upper surface edge of the chip 1 so as to form a cavity 13 between the transparent cover plate 2 and the image sensor chip 1, and the support bank 4 and the image sensor chip 1 are bonded by a glue layer 5 In combination, there are several blind holes 6 distributed around the edge area around the lower surface of the image sensor chip 1, the lower surface of the image sensor chip 1 and the side surfaces of the blind holes 6 have a passivation layer 7, and the bottom of the blind hole 6 has an image sensor The pin pad 8 of the sensor chip 1, the surface of the passivation layer 7 opposite to the image sensor chip 1 and the blind hole 6 have a metal conductive pattern layer 9 ele...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com