Array substrate, preparing method thereof and display device

A technology of array substrates and substrate substrates, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve problems such as poor light transmittance, increase production costs, and reduce production efficiency, so as to reduce the manufacturing process steps, save production costs, and improve production efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0044] Such as Figure 4 As shown, the present invention provides a method for preparing an array substrate, comprising the following steps:

[0045] S1. forming a pattern comprising a gate, a gate insulating layer, an active layer, and source and drain electrodes on the base substrate;

[0046] Specifically, in the process of manufacturing the array substrate, the gate electrode, the source electrode, and the drain electrode are made of conductive materials such as metal, and the active layer is made of amorphous silicon (a-Si). The gate insulating layer adopts SiO2, SiN x and other transparent amorphous oxides; the gate, gate insulating layer, active layer, source and drain are respectively produced through a patterning process.

[0047] Further, in step S1, a gate is formed on the base substrate, and a gate line and a gate line connecting line are also formed at the same time.

[0048] S2. Form a transparent conductive layer on the base substrate after step S1, and simul...

Embodiment 1

[0054] This embodiment provides a method for preparing an array substrate, and the specific method is as follows:

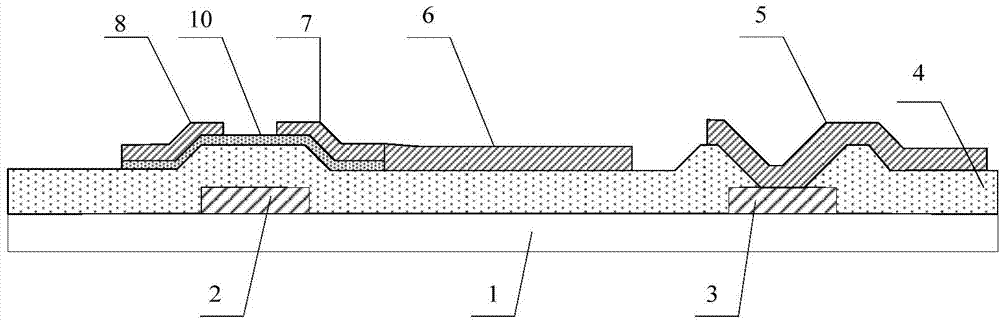

[0055] S1. If figure 1 As shown, a pattern comprising a gate 2, a gate insulating layer 4, an active layer 10, a source 8 and a drain 7 is formed on a base substrate 1;

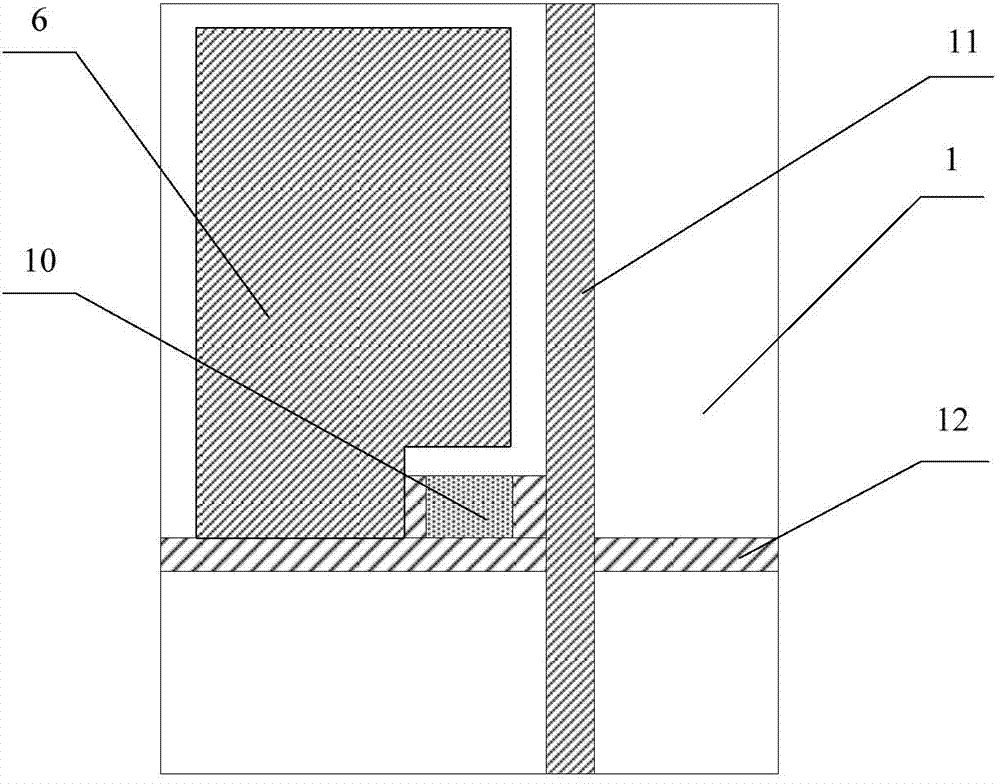

[0056] Further, in step S1, while forming the gate 2, also form such as image 3 grid lines 12 as shown and as figure 1 The grid line connection line 3 shown;

[0057] Specifically, in the process of manufacturing the array substrate, the gate electrode, the source electrode, and the drain electrode are made of conductive materials such as metal, and the active layer is made of amorphous silicon (a-Si). The gate insulating layer adopts SiO2, SiN x and other transparent amorphous oxides; the gate line, the gate line connection line, the gate, the gate insulating layer, the active layer, the source electrode and the drain electrode are respectively manufactured through a patterning process.

...

Embodiment 2

[0073] This embodiment provides a method for preparing an array substrate, including the following steps:

[0074] S1. If figure 1 As shown, a gate 2, a storage capacitor bottom electrode 3, a gate insulating layer 4, an active layer 10, a source 8 and a drain 7 are formed on a substrate 1;

[0075] Further, in step S1, while forming the gate 2, also form such as image 3 grid lines 12 as shown and as figure 1 The grid line connection line 3 shown;

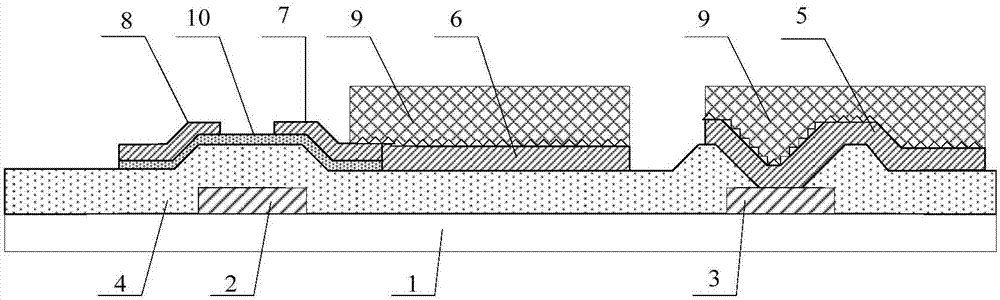

[0076] S2. On the base substrate 1 of step S1, a transparent conductive layer of graphene material is continuously deposited by sputtering; a transparent conductive layer pattern comprising pixel electrodes 6 and data lines 11 is formed simultaneously through a patterning process (or A pattern including the data line, the pixel electrode and the protective layer 5 for protecting the connecting line 3 of the gate line is simultaneously formed through one patterning process).

[0077] Step S2 specifically includes:

[0078] A t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com