Semiconductor treatment technology and semiconductor device preparation method

一种处理工艺、半导体的技术,应用在半导体器件、半导体/固态器件制造、晶体管等方向,能够解决影响嵌入硅锗器件性能等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0054] Further, the above-mentioned semiconductor processing technology can be applied to a method for preparing a semiconductor device, and the method for preparing a semiconductor device includes:

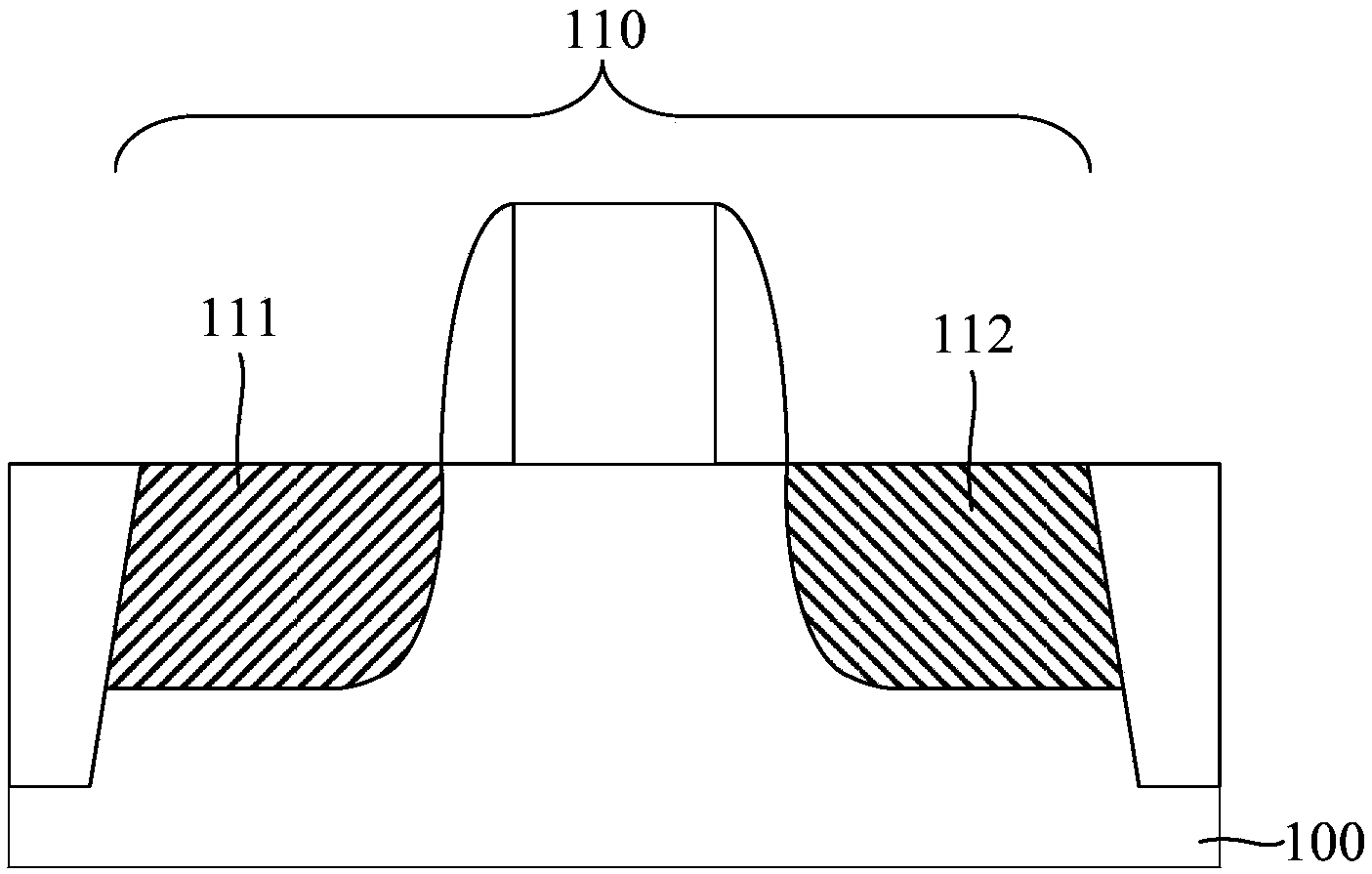

[0055] providing a substrate (corresponding to the base in the semiconductor processing process), on which a groove is etched in the part where the source and drain regions are to be formed;

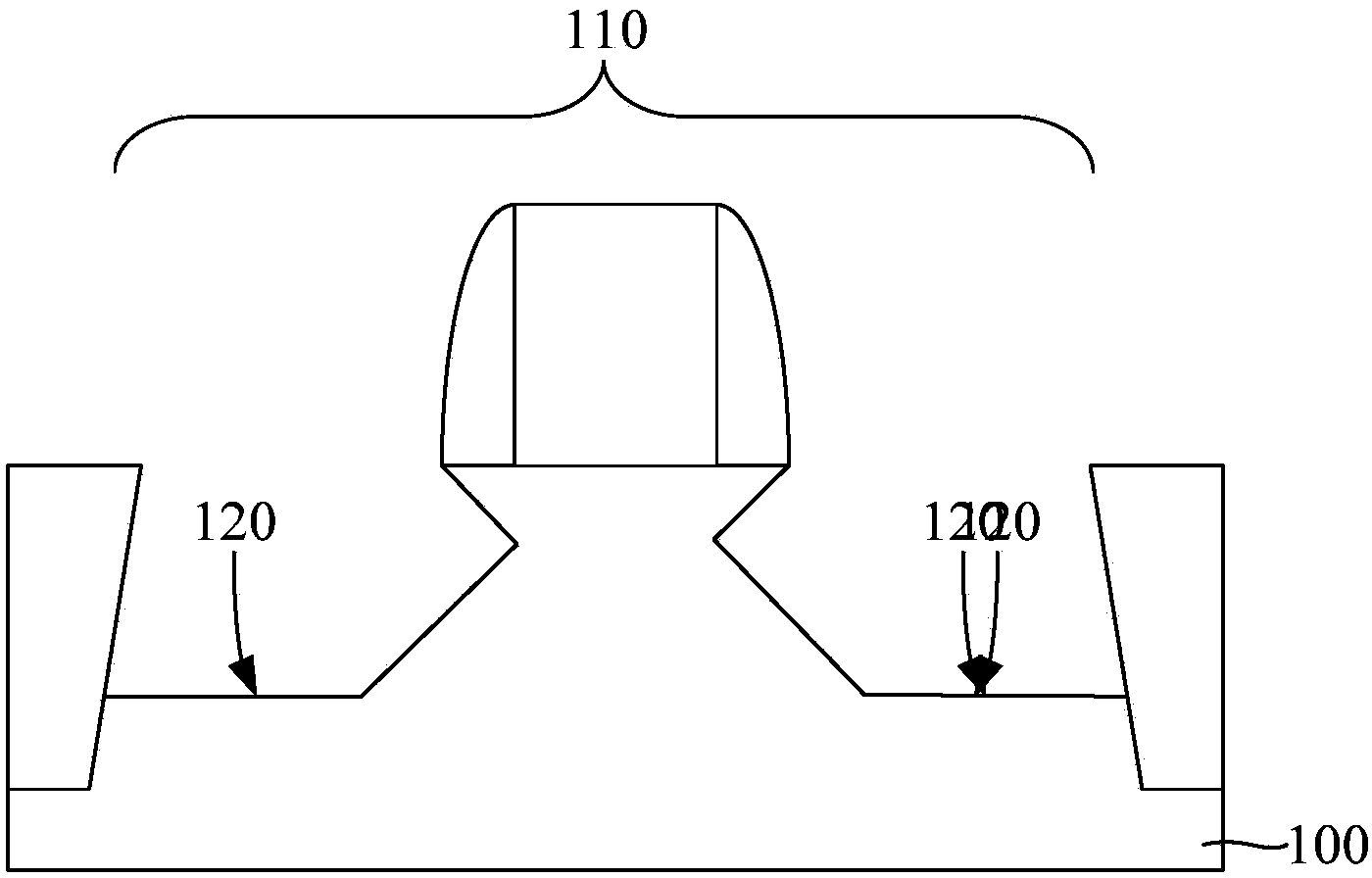

[0056] performing at least one oxidation-deoxidation treatment on the groove;

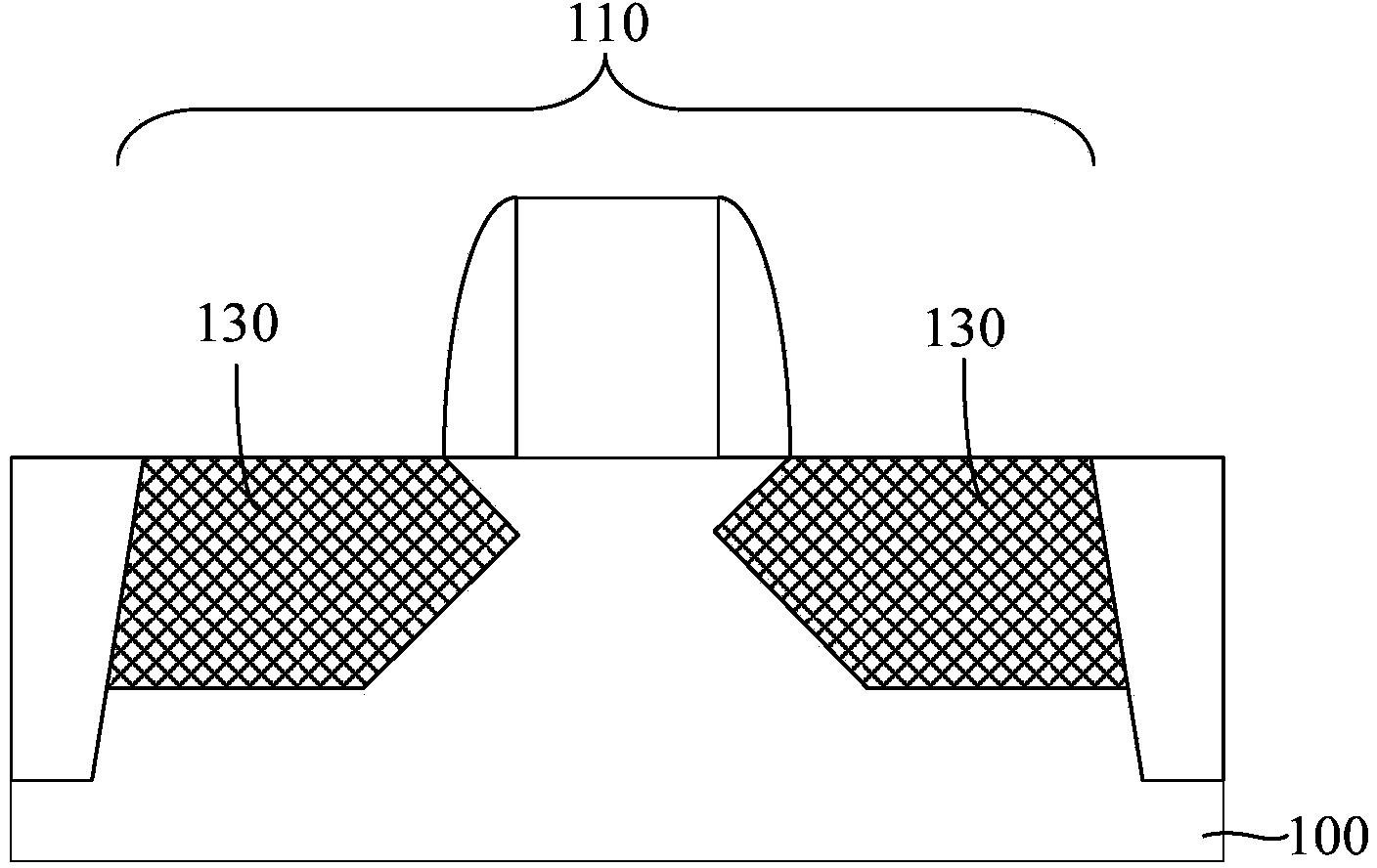

[0057] forming a strain-inducing layer in the groove; wherein,

[0058] Described oxidation-reoxidation treatment comprises:

[0059] Oxidizing the surface of the groove to form an oxide layer on the surface of the groove;

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com