Semi-conductor device with self-aligning contact holes and manufacture method of semi-conductor device

A self-aligned contact hole, semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve problems such as no effective means proposed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

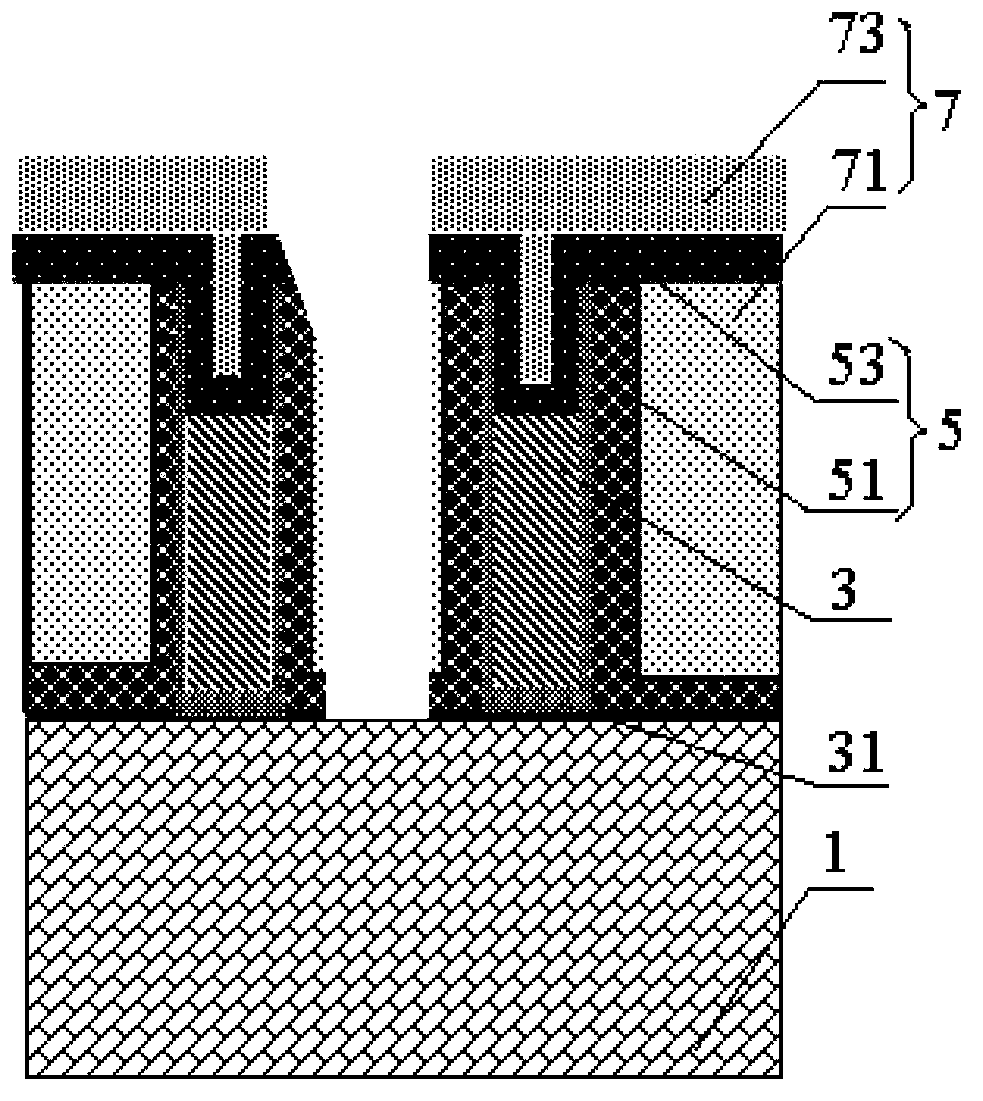

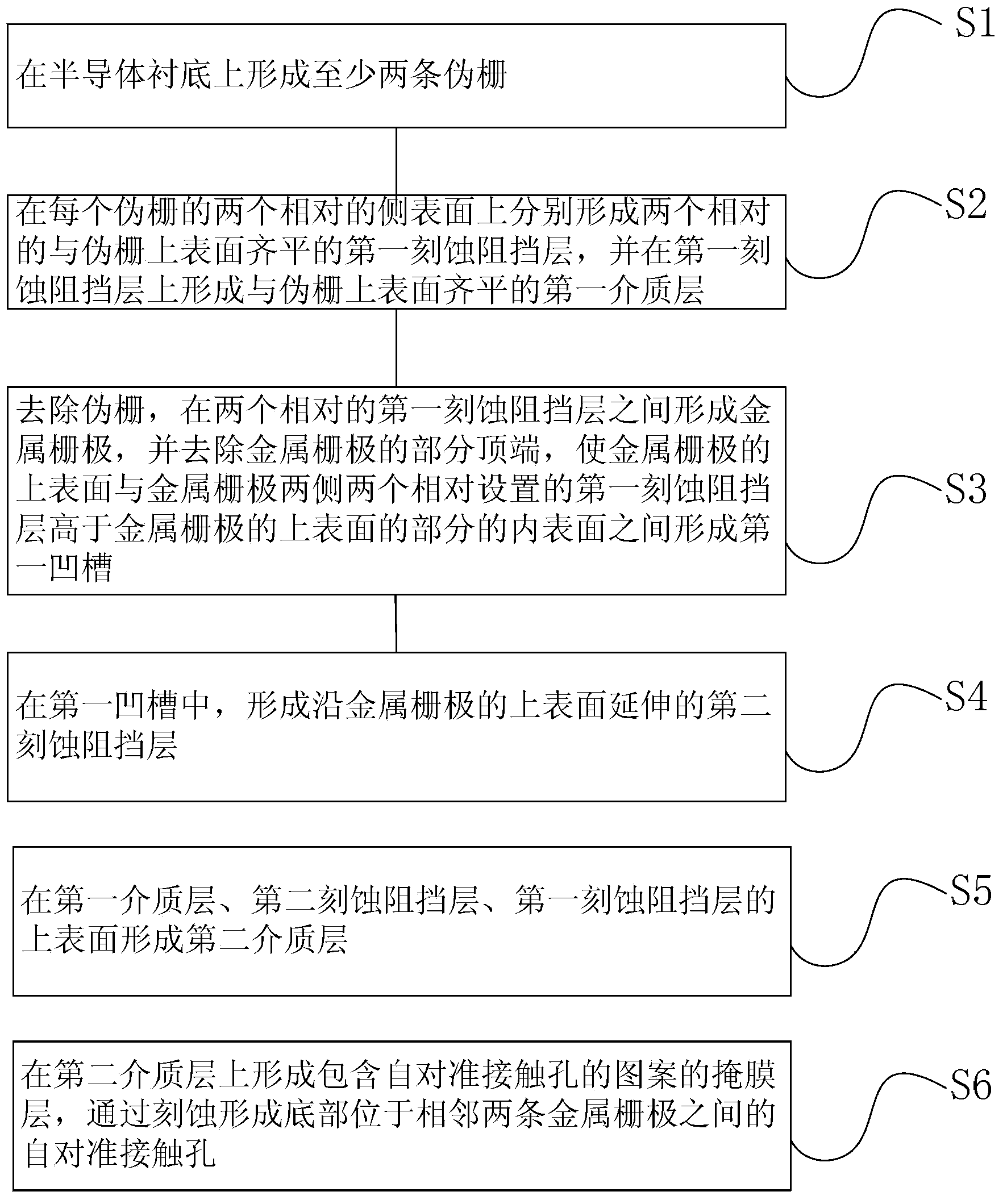

[0061] At the same time, in an embodiment of the present application, a method for preparing a semiconductor device with self-aligned contact holes is also provided, such as figure 2 As shown in the flow chart, the method includes the following steps: S1, forming at least two dummy gates 3' on the semiconductor substrate 1. S2. On the two opposite side surfaces of each dummy gate 3′, respectively form two opposite first etch barrier layers 51 flush with the upper surface of the dummy gate 3′, and form on the first etch barrier layer 51 A first dielectric layer 71 flush with the upper surface of the dummy gate 3′. S3, remove the dummy gate 3', form the metal gate 3 between the two opposite first etching barrier layers 51, and remove part of the top of the metal gate 3, so that the upper surface of the metal gate 3 is aligned with the metal gate 3 A first groove is formed between the inner surfaces of the portions of the first etch barrier layer 51 disposed opposite to each ot...

Embodiment 1

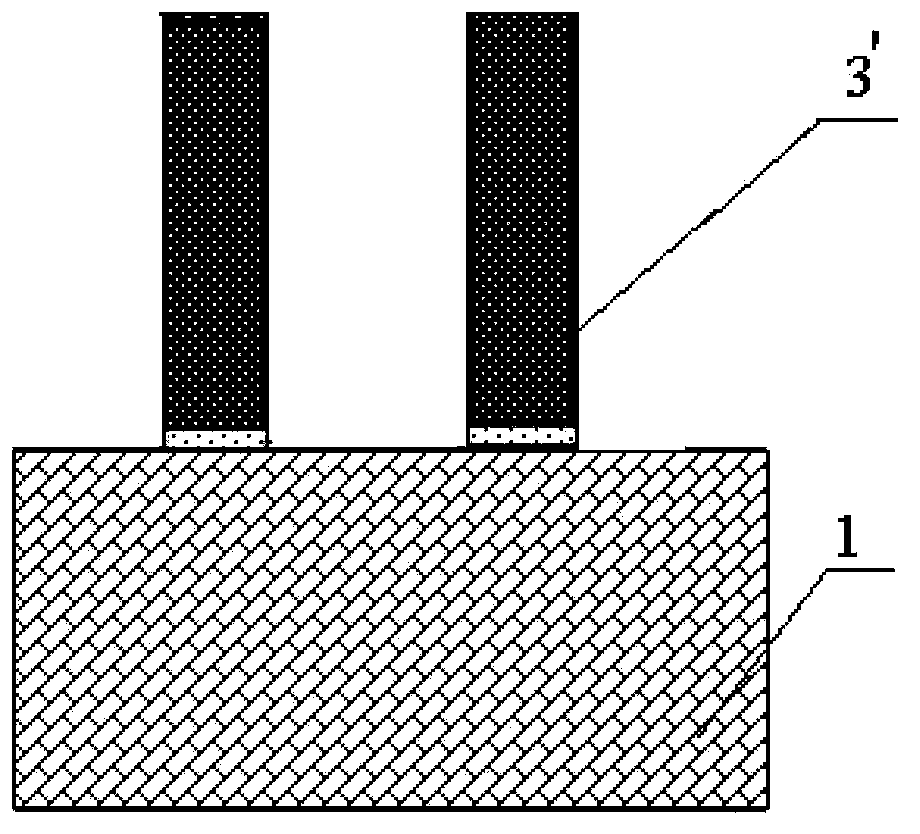

[0075] The following will combine Figure 3a to Figure 3d The specific operation steps of an embodiment of the method for manufacturing a semiconductor device with self-aligned contact holes according to the present application will be described in detail. Figure 3a to Figure 3d A schematic cross-sectional structure diagram of a substrate in each step in the first embodiment of the method for manufacturing a semiconductor device according to the present application is shown.

[0076] S1, such as Figure 3a As shown, at least two dummy gates 3' are formed on the semiconductor substrate 1. Wherein, the substrate 1 may be a single crystal silicon or a polycrystalline silicon substrate, and may also be a silicon-on-insulator, and a source electrode and a drain electrode (not shown in the figure) are formed in the substrate 1 . The formed dummy gate 3' is a gate made of polysilicon material. In actual operation, before forming the dummy gate 3', a dummy gate dielectric layer ma...

Embodiment 2

[0089] A method for preparing a semiconductor device with self-aligned contact holes comprises the following steps:

[0090] Steps S1 to S3 are the same as in Embodiment 1.

[0091] Step S4, using the SiN material with a high selective etching ratio of 8 to the first dielectric layer 71, to form a second etch that extends continuously on the upper surfaces of the metal gate 3, the first etch stop layer 51, and the first dielectric layer 71. etch stop layer 53. The second etch barrier layer 53 is formed by chemical vapor deposition.

[0092] Step S5 , forming a second dielectric layer 73 on the upper surface of the second etch stop layer 53 . The material of the formed second dielectric layer 73 is an insulating material with a low dielectric constant. The second dielectric layer 73 is formed by chemical vapor deposition. After the second dielectric layer 73 is deposited, chemical mechanical polishing can be used to planarize the surface.

[0093] Step S6, the step of form...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com