Frame based flat package part manufacturing process adopting cutting channel optimization technology

A technology of flat packaging and manufacturing process, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., and can solve problems such as defective products, reduced product packaging reliability, and delamination

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The invention will be further described below according to the accompanying drawings.

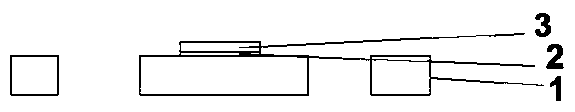

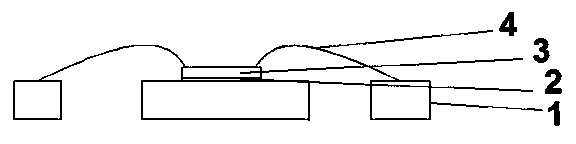

[0025] Such as Figure 8 As shown, a frame-based flat package is mainly composed of a lead frame 1 , a die-bonding glue 2 , a chip 3 , a bonding wire 4 and a plastic package 5 . The lead frame 1 and the chip 3 are connected by the adhesive 2 , the bonding wire 4 connects the lead frame 1 and the chip 3 , and the plastic package 5 surrounds the lead frame 1 , the adhesive 2 , the chip 3 and the bonding wire 4 . The plastic package 5 supports and protects the chip 3 and the bonding wire 4 . The chip 3, the bonding wire 4, the plastic package 5, and the lead frame 1 constitute the power supply and signal channel of the circuit.

[0026] The process flow of a flat package based on frame-based dicing line optimization technology is as follows: wafer thinning→scribing→die (bonding)→bonding→plastic sealing→post-curing→etching dicing lines→cutting→inspection→packaging → Storage.

[0027]...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com