Laterally diffused low on-resistance MOS devices

A low on-resistance, MOS device technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of reducing volume and large layout area, and achieve the effects of reducing power consumption, increasing design space, and increasing gate width

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

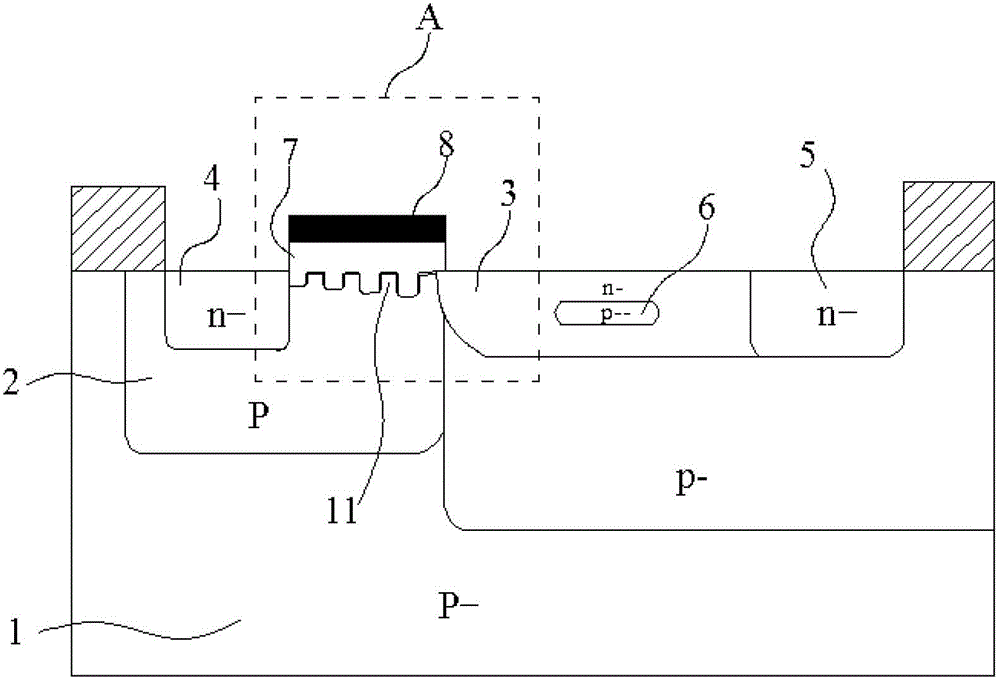

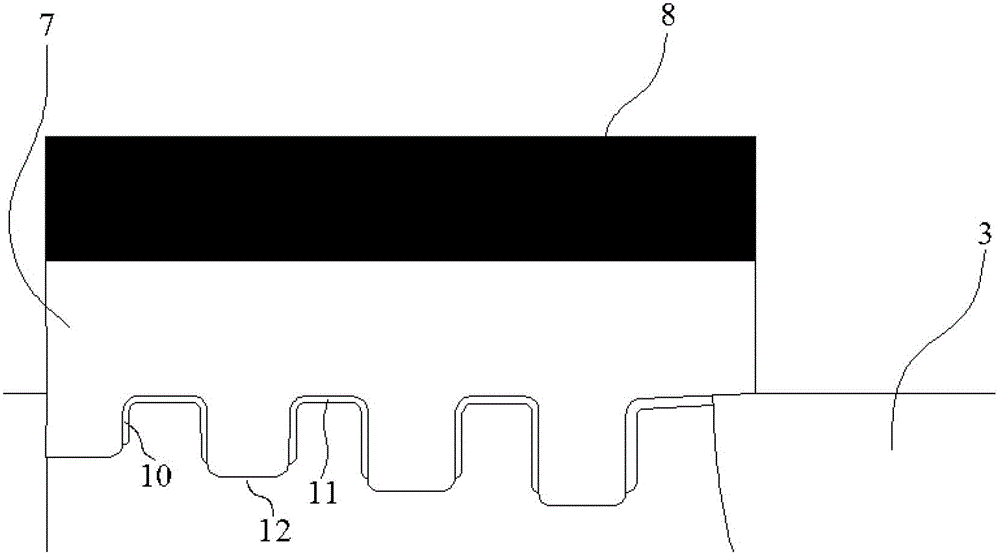

[0019] Embodiment 1: A lateral diffusion type low on-resistance MOS device, comprising: a P-type well layer 2 and an N-type lightly doped layer 3 in a P-type substrate layer 1, the P-type well layer 2 and N Type lightly doped layers 3 are adjacent in the horizontal direction to form a PN junction, a source region 4 is located in the P-type well layer 2, a drain region 5 is located in the substrate layer 1, and is located in the source region A gate oxide layer 7 is provided above the P-type well layer 2 in the region between the region 4 and the N-type lightly doped layer 3, and a gate region 8 is provided above the gate oxide layer 7; the source region 4 and the N-type lightly doped layer At least two grooves 9 are opened between the impurity layers 3 and located on the upper part of the P-type well layer 2, and the groove 9 near the source region 4 has a smaller etching depth than the groove 9 near the N-type lightly doped layer 3. Etching depth, and the etching depth of the ...

Embodiment 2

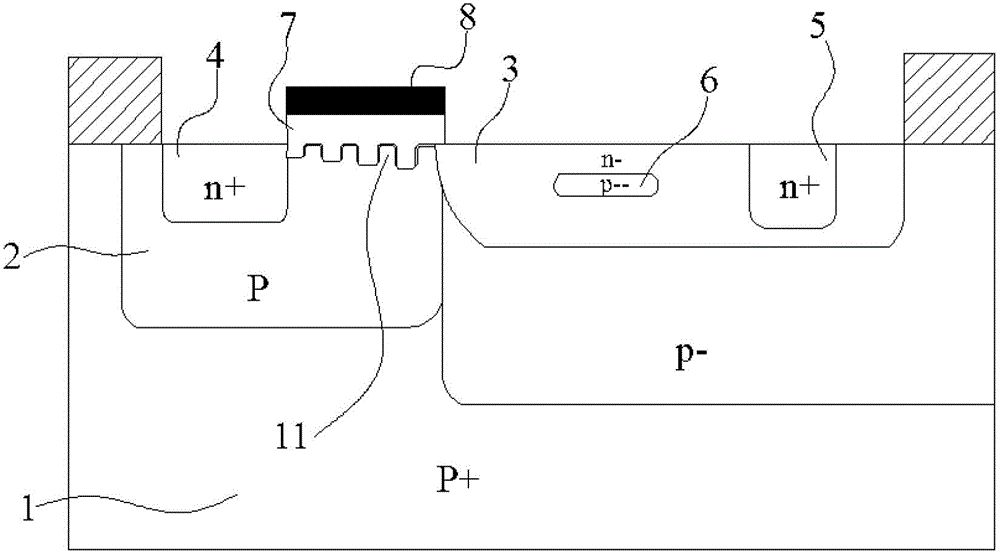

[0024] Embodiment 2: A lateral diffusion type low on-resistance MOS device, comprising: a P-type well layer 2 and an N-type lightly doped layer 3 located in a P-type substrate layer 1, the P-type well layer 2 and N Type lightly doped layers 3 are adjacent in the horizontal direction to form a PN junction, a source region 4 is located in the P-type well layer 2, a drain region 5 is located in the substrate layer 1, and is located in the source region A gate oxide layer 7 is provided above the P-type well layer 2 in the region between the region 4 and the N-type lightly doped layer 3, and a gate region 8 is provided above the gate oxide layer 7; the source region 4 and the N-type lightly doped layer At least two grooves 9 are opened between the impurity layers 3 and located on the upper part of the P-type well layer 2, and the groove 9 near the source region 4 has a smaller etching depth than the groove 9 near the N-type lightly doped layer 3. Etching depth, and the etching depth...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com