Block RAM (random-access memory) with multiple Write-Modes in FPGA (field programmable gate array)

A technology for writing patterns and input bits, which is applied in information storage, static memory, digital memory information, etc., can solve problems affecting chip operating frequency, large skew time, reliability errors, etc., to achieve both high speed and reliability, The effect of guaranteeing functional correctness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

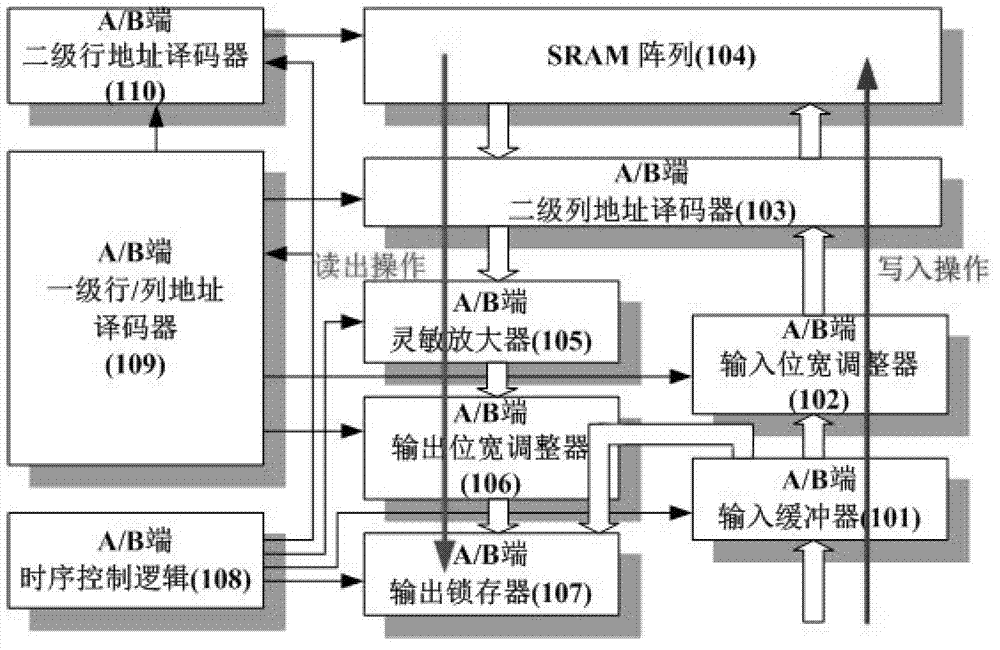

[0022] For output data, the most important timing is in the second column decoding module 103 and sensitive amplifier modules 105 superior. Because the secondary column decoding module 103 is a bidirectional channel for selective input / output of control data, while the sensitive amplifier module 105 It is to differentially amplify the analog waveform signal read from the SRAM to generate a standard digital signal and latch it, so as to ensure the correct transmission of data.

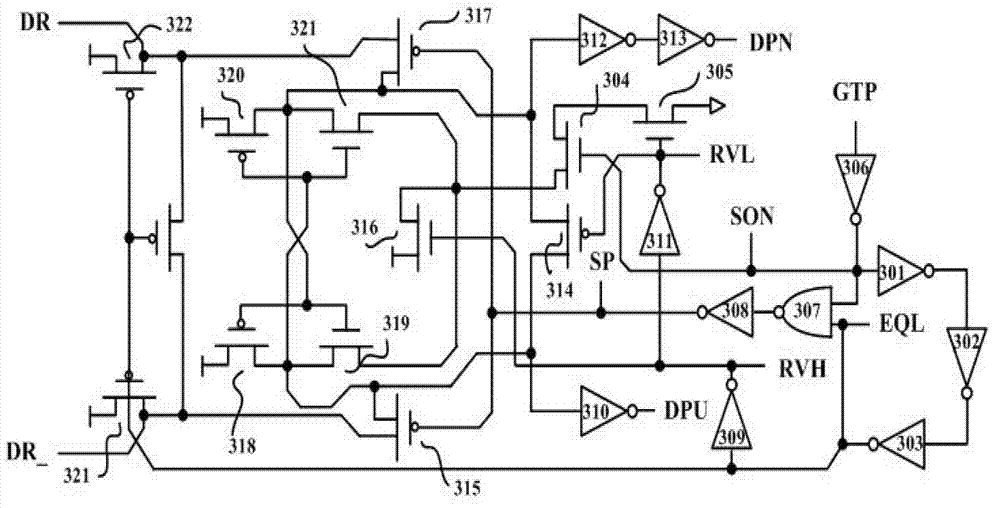

[0023] Sensitive Amplifier Module 105 Such as image 3 shown. The combined circuit part on the right is used to generate various control signals, mainly controlling the delay between signal circuits. Of particular note are the three rightmost inverters ( 301 , 302 , 303 ), which is used to generate a delay so that the SON signal turns on the corresponding MOS tube earlier than the RVL signal. The situation in which this is done is that the two sets of NMOS transistors ( 305 , 306 ) only in t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com