Wafer testing method used for design analysis purpose

A technology of wafer testing and design analysis, applied in the field of wafer testing, can solve problems such as poor needle stability, damaged chips, unstable signals, etc., and achieve the effect of improving the efficiency of detection signals

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

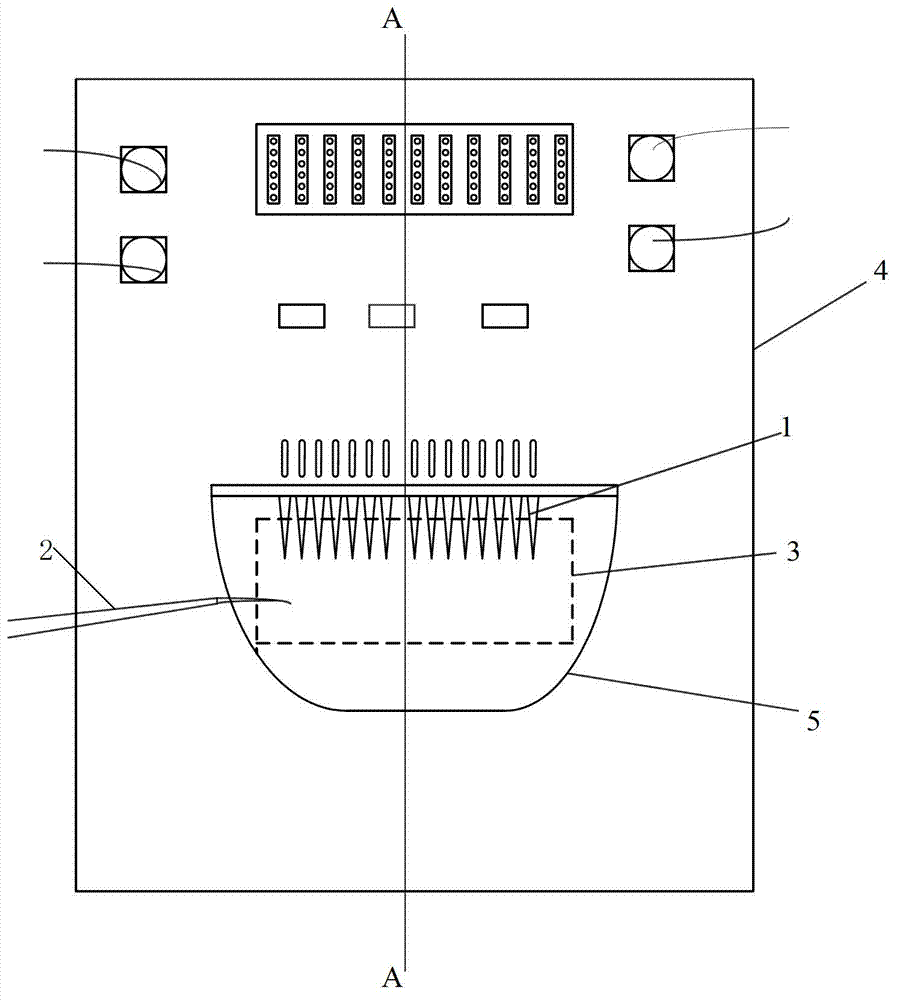

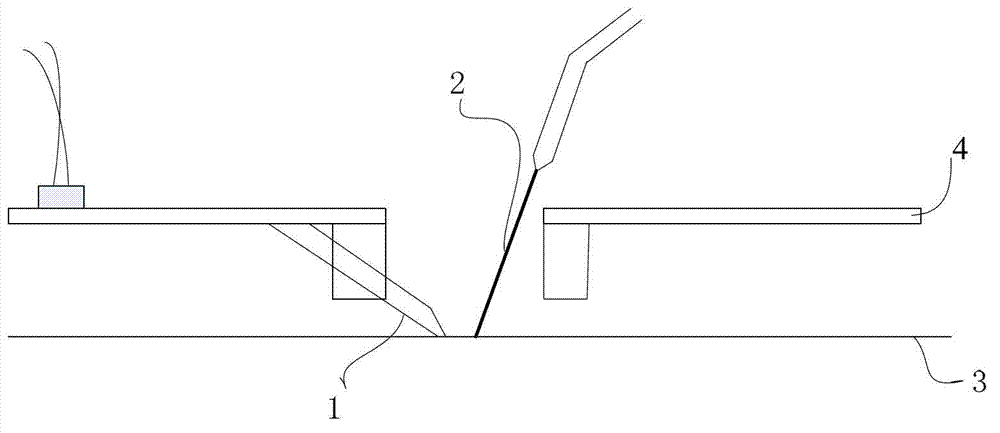

[0030] Below in conjunction with accompanying drawing, content of the present invention is elaborated:

[0031] refer to image 3 , the present invention provides a wafer test method for design and analysis purposes, a redistribution layer 13 is made on the finished wafer, and some first pads of chips in the wafer are connected to the redistribution layer through the redistribution layer connecting wires. Several second pads corresponding to the first pads on the layer are connected, and the second pads of the redistribution layer 13 are located outside the area probed by the microprobe, for example: a position that does not need to be probed inside the chip, or between a chip and a chip. In between, or near the top of the chip, use the probe card to test the wafer at the second pad position of the redistribution layer, and use the micro-probe on the chip to perform signal testing on the chip. The needles of the card are separated, thereby effectively increasing the contact a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com