Parallel Synthesis Method and System for Integrated Circuit Design

A technology of integrated circuits and synthesis methods, applied in the field of parallel synthesis methods and systems, can solve the problems of inability to generate circuits, not taking into account the various deformation structures of CDFG at the same time, and long computer running time, etc., to achieve the effect of shortening the time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] In the following description, many technical details are proposed in order to enable readers to better understand the application. However, those skilled in the art can understand that without these technical details and various changes and modifications based on the following implementation modes, the technical solution claimed in each claim of the present application can be realized.

[0033] In order to make the purpose, technical solution and advantages of the present invention clearer, the following will further describe the implementation of the present invention in detail in conjunction with the accompanying drawings.

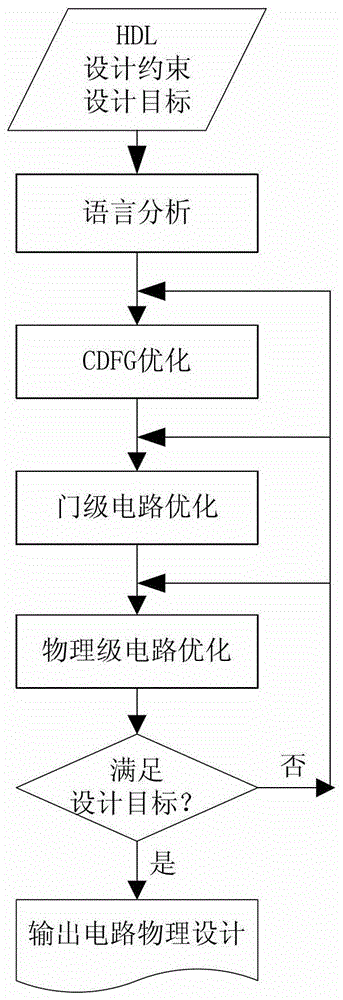

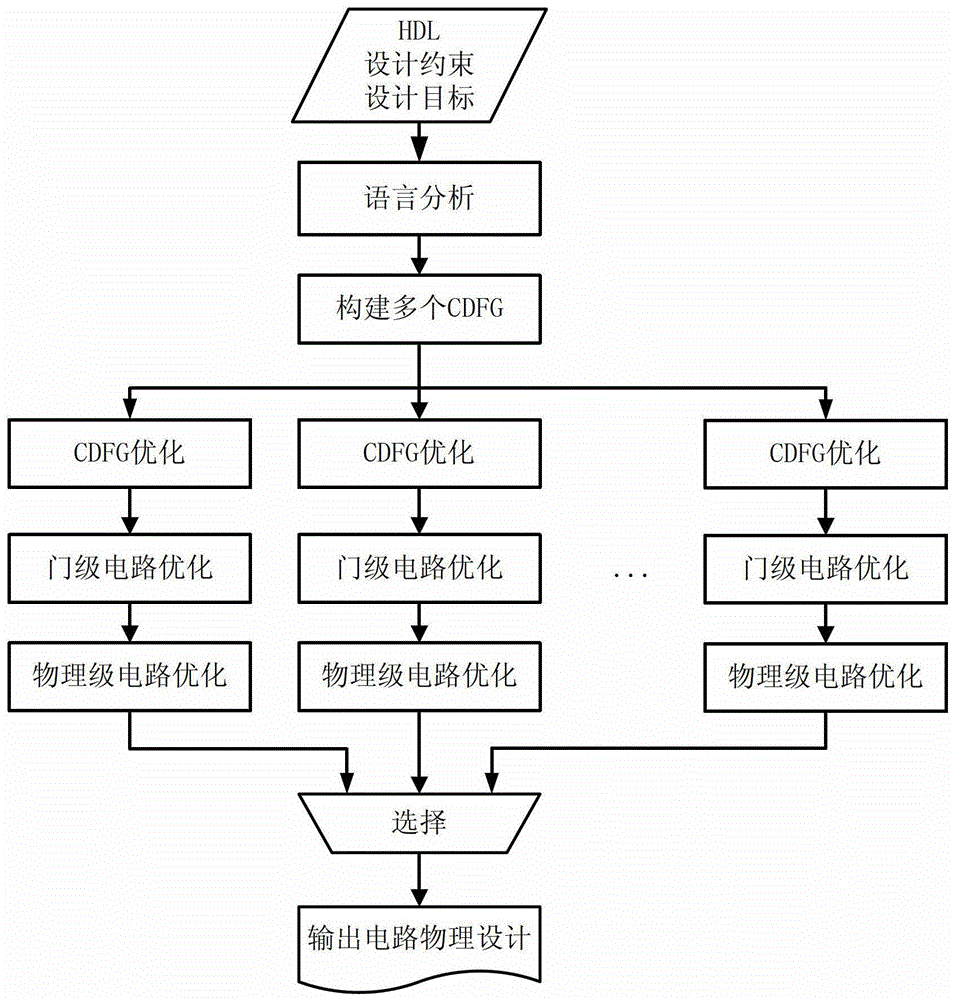

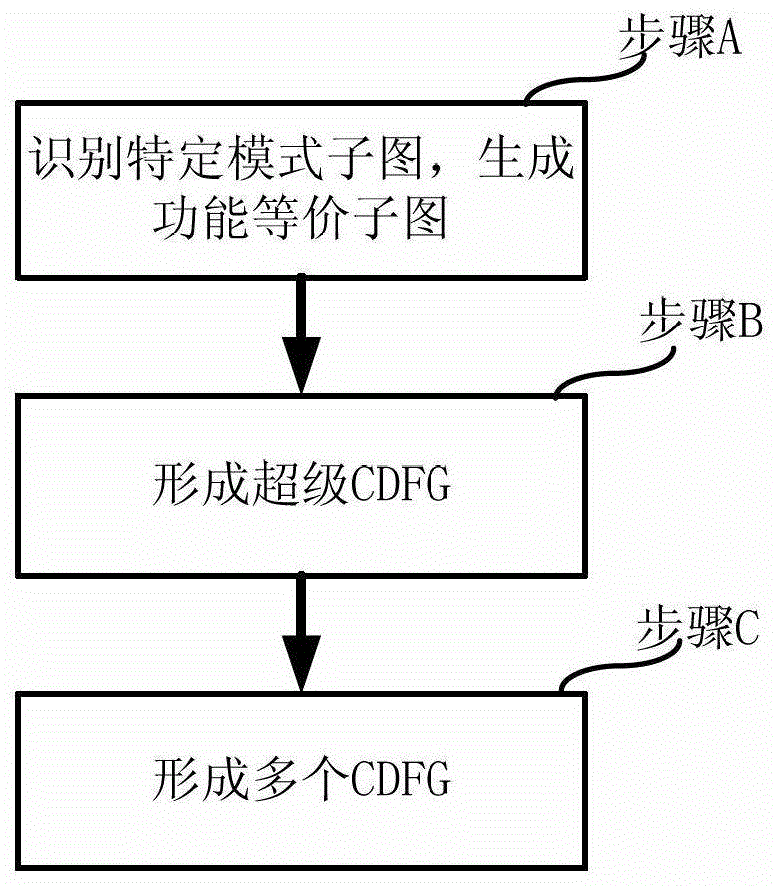

[0034] The first embodiment of the present invention relates to a parallel synthesis method for integrated circuit design. figure 2 is a flow diagram of the parallel synthesis method. The above synthesis is to transform the high-level hardware description into a low-level hardware description, such as figure 2 As shown, the method includes the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com