Programmable non-overlapping clock generation circuit and work method thereof

A clock generation circuit, non-overlapping technology, applied in the direction of single pulse train generator, etc., can solve problems such as changing delay, and achieve the effect of expanding the scope of application

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

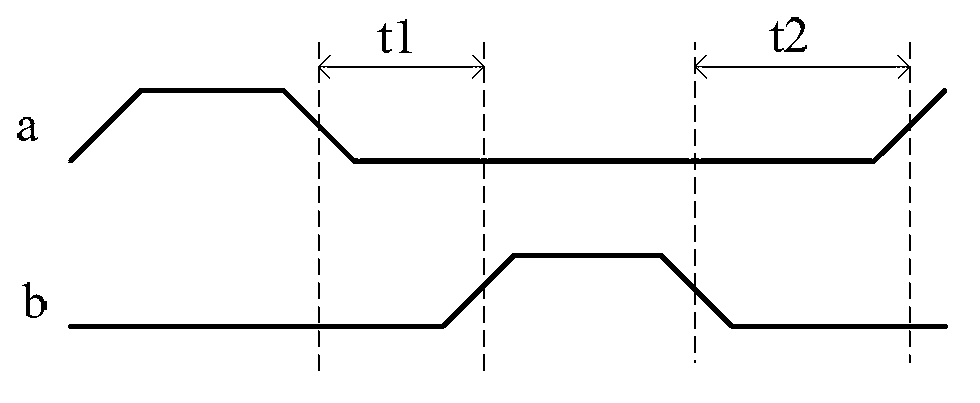

[0048] Such as Image 6 , 7 , 8 shown.

[0049] A programmable non-overlapping clock generation circuit, comprising two signal branches and an inverting module 3, branch A in the two signal branches, comprising a logic module 11, a delay module 12 and a series connection Select the control module 13, the selection control module 13 is connected to the signal output terminal clka; the branch B in the two signal branches includes a logic module 21, a delay module 22 and a selection control module 23 connected in series, the The selection control module 23 is connected to the signal output terminal clkb; the signal input terminal clk is connected to the input terminal of the inverting module 3 and an input terminal of the logic module 11, and the other input terminal of the logic module 11 is connected to the signal output terminal clkb ; The output terminal of the inverting module 3 is connected to an input terminal of the logic module 21, and the other input terminal of the l...

Embodiment 2

[0063] A working method of a programmable non-overlapping clock generating circuit as described in Embodiment 1, comprising the steps as follows:

[0064] 1) The signal is input to the programmable non-overlapping clock generation circuit along the signal input terminal clk;

[0065] 2) In the delay programmable control module 132, by encoding the control bit of the feedback point selection module 131: select the i1th series node in the delay module to connect with the input terminal on the feedback point selection module 131, where i1 is greater than or equal to 1 and an integer less than or equal to n, then the total delay of the signal in branch A is i1×T;

[0066] In the delay programmable control module 232, by coding the control bit of the feedback point selection module 231: select the i2th series node in the delay module to communicate with the input on the feedback point selection module 231, wherein i2 is greater than or equal to 1 and less than is an integer equal ...

Embodiment 3

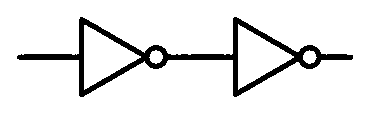

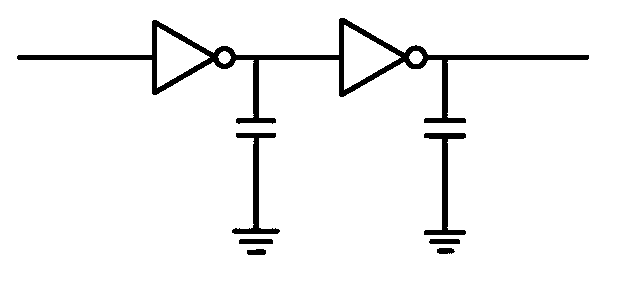

[0072] The circuit described in Embodiment 1 is different in that the delay unit includes two inverters connected in series, and the output terminal of each inverter is respectively connected to a capacitor and grounded. Such as image 3 shown.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com