Chip provided with multiplex pin

A technology of multiplexing pins and chips, applied in the direction of logic circuit connection/interface layout, etc., can solve the problems of increasing package size, high packaging cost, unfavorable miniaturization design, etc., and achieve the goal of reducing pins and packaging area Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] In order to make the above objectives, features and advantages of the present invention more obvious and understandable, the present invention will be further described in detail below with reference to the accompanying drawings and specific embodiments.

[0024] The "one embodiment" or "embodiment" referred to herein refers to a specific feature, structure, or characteristic that can be included in at least one implementation of the present invention. The appearances of "in one embodiment" in different places in this specification do not all refer to the same embodiment, nor are they separate or selectively mutually exclusive embodiments with other embodiments. Unless otherwise specified, the words connected, connected, and connected in this text indicating electrical connection all mean direct or indirect electrical connection.

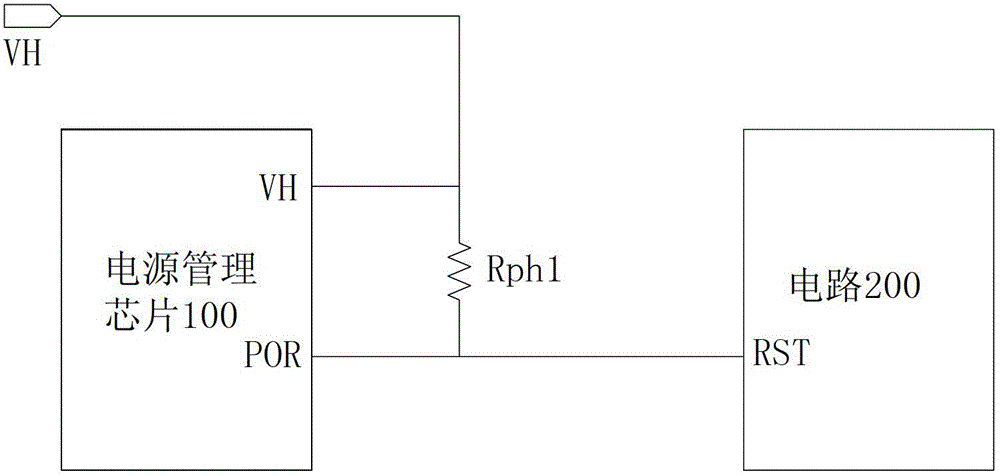

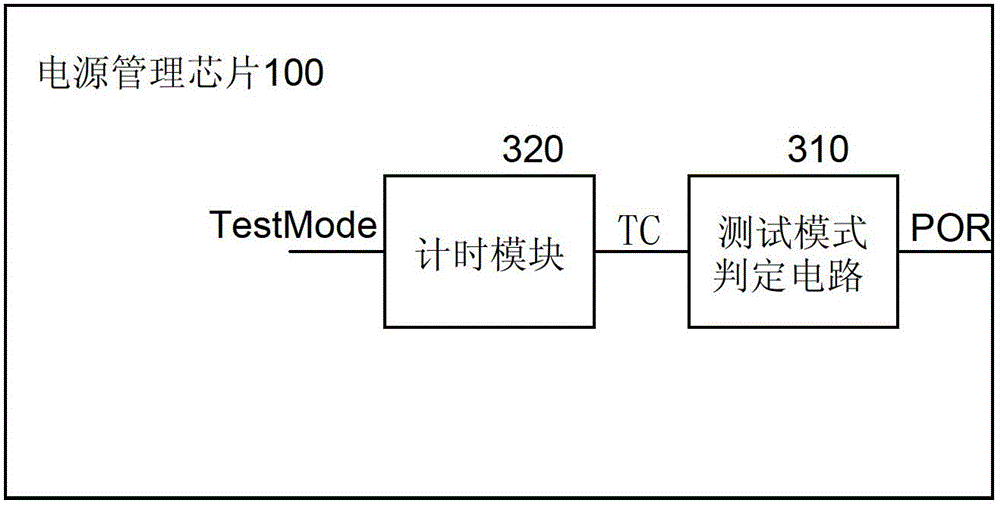

[0025] In the present invention, the test pin is multiplexed with another pin, so that the power management chip has a test mode without adding c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com