Embedded non-volatile memory provided with P+ single polycrystalline architecture of selector transistor and free of light doped regions and preparation method of embedded non-volatile memory

A non-volatile, transistor-based technology, applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve the problem of large ratio of control circuit area, achieve compact structure, reduce processing costs, and improve adaptability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

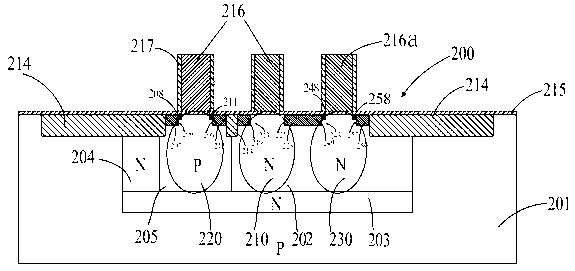

[0068] like figure 1 and Figure 13 Shown: In order to make the non-volatile memory compatible with the CMOS logic process and enable the non-volatile memory to store for a longer period of time, the non-volatile memory includes a P conductivity type substrate 201, a P conductivity type substrate 201 The material is silicon. The upper part of the P conductivity type substrate 201 is provided with at least one memory cell 200, and the memory cell 200 includes a PMOS transistor 210 without a lightly doped region, a control capacitor 220 and a PMOS selector transistor 230, and the P conductivity type substrate 201 A gate dielectric layer 215 is deposited and covered on the surface, and the gate dielectric layer 215 covers the surface corresponding to the formation of the memory cell 200, and the area between the PMOS transistor 210 and the control capacitor 220 without the lightly doped area passes through the area in the P conductivity type substrate 201 The dielectric region ...

Embodiment 2

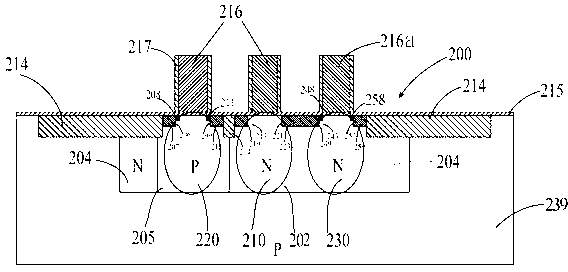

[0094] like figure 2 and Figure 23 As shown: in this embodiment, the semiconductor substrate is an N-conductive type substrate 239. When the N-conductive type substrate 239 is used, there is no need to form the second N-type region 203 and the second P-type region 205 in the N-conductive type substrate 239 to directly contact with the second P-type region 205. The N-type conductive type substrate 239 is in contact with, and at the same time, the first N-type region 202 and the third N-type region 204 are also in direct contact with the N-type conductive type substrate 239 . After adopting the substrate 239 of N conductivity type, the rest of the structure is the same as that of Embodiment 1.

[0095] like Figure 14~Figure 23 Shown: the non-volatile memory of the above structure can be realized through the following process steps, specifically:

[0096] a. An N conductive type substrate 239 is provided, and the N conductive type substrate 239 includes a first main surface...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com