Wafer level packaging structure with large contact area and preparation method thereof

A wafer-level packaging and contact surface technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc. Small size and other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

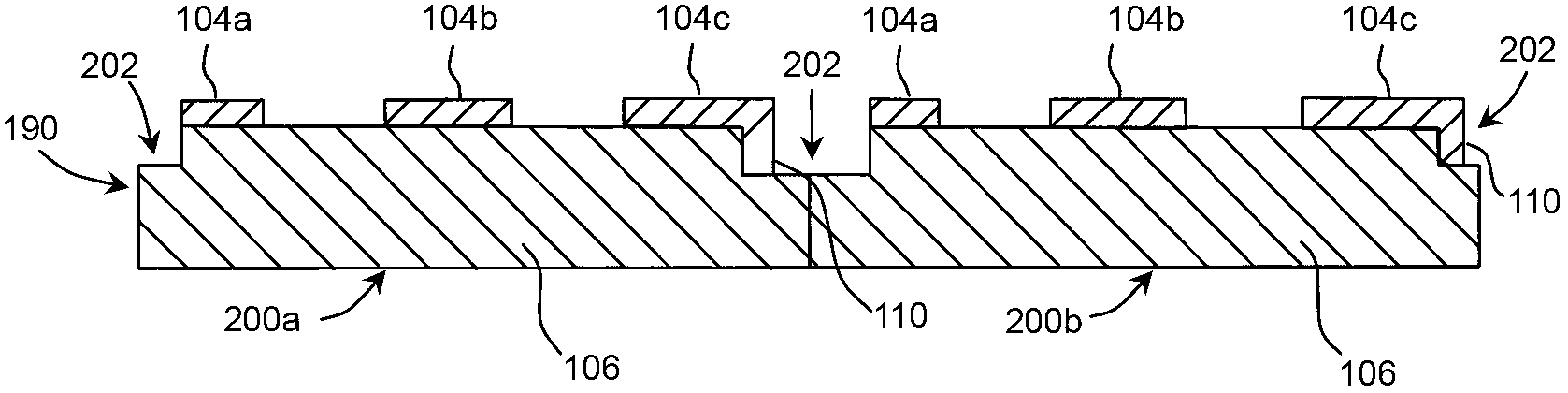

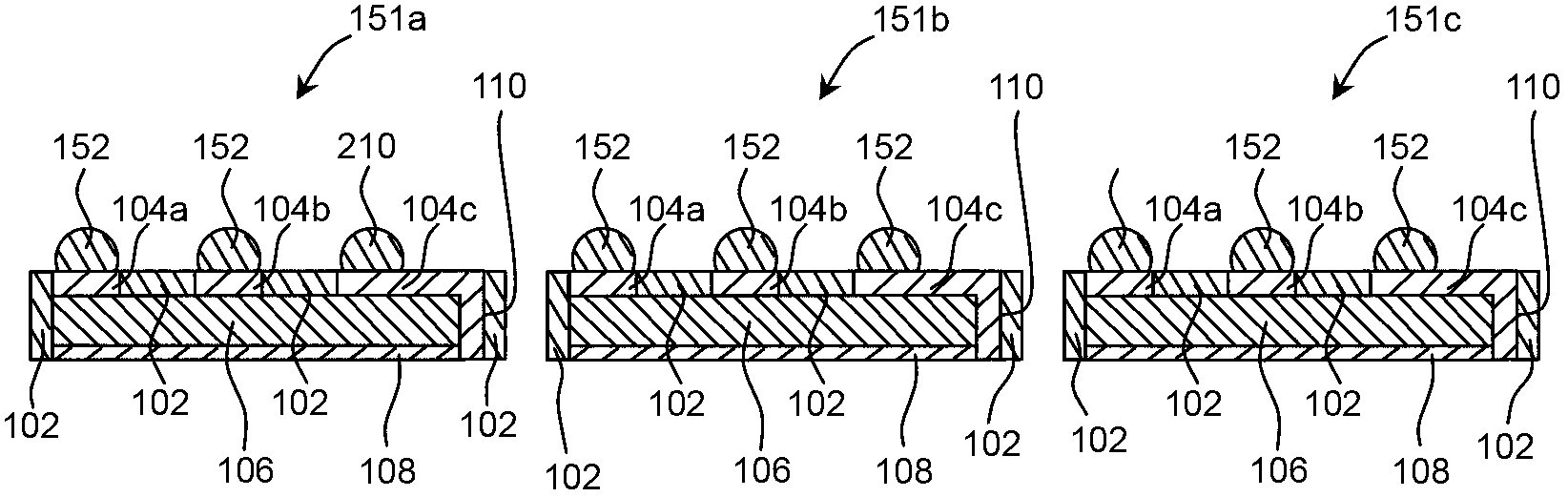

Embodiment Construction

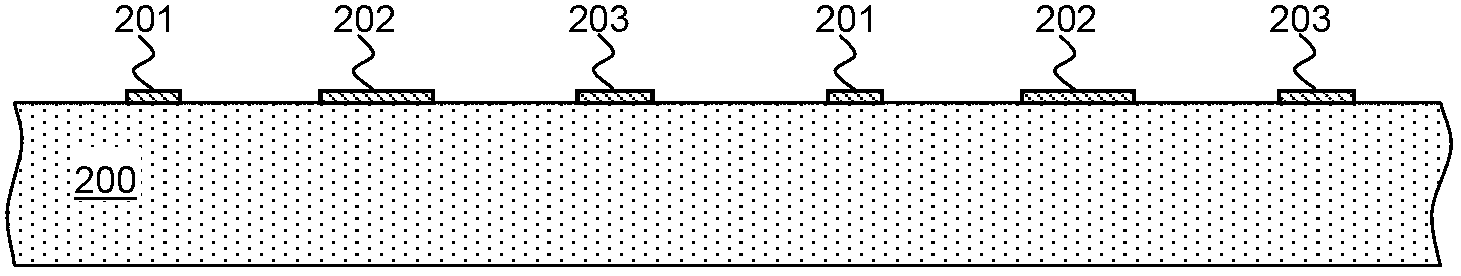

[0052] see Figure 2A , the wafer 200 usually contains a large number of chips connected together by casting, and the boundary between adjacent chips is defined by an unillustrated scribe line (Scribe line), and finally the chips can be removed from the wafer 200 along the scribe line. Cutting and separation, since these technical features are well known to those skilled in the art, the present invention is no longer Figure 2A Chips are intentionally marked additionally. Under known technical conditions, after the normal preparation process of the wafer 200 is completed, a plurality of first-type metal pads 201, 202 are usually prepared on the front side of the wafer 200. The front side of any one of the included chips is prepared with first-type metal pads 201 , 202 . The first type of metal pads 201, 202 are usually aluminum-silicon metal pads (I / O Pads) pre-designed on the chip, and the first type of metal pads 201, 202 are usually used as electrodes of the chip or with ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com