NOR memory cell based on resistance-changeable gate dielectric, its array and its operation method

A technology of memory cells and gate dielectrics, applied in the field of memory, can solve problems such as thinning of floating gates, and achieve the effects of low power consumption, simple process and high performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

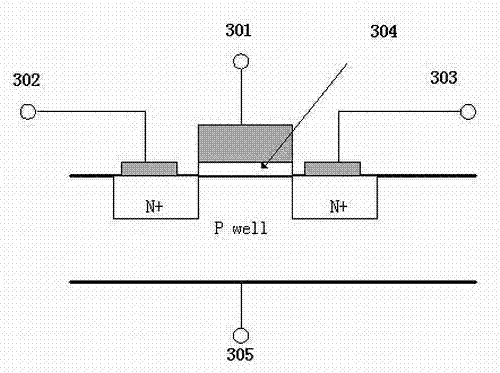

[0024] According to an embodiment of the present invention, the NOR memory based on the resistive gate dielectric includes: a transistor, including a source, a drain, and a control gate; a storage node, that is, the gate dielectric of the transistor control gate, located between the transistor control gate and Among the silicon substrates, the storage resistance changes; the word line is connected to the control gate of the transistor; the bit line is connected to the drain of the transistor; the source line is connected to the source of the transistor. Reference attached image 3 , is a NOR memory cell based on a resistive gate dielectric according to an embodiment of the present invention. Wherein, 301 is a word line (Wordline), 302 and 303 are respectively a source line (Sourceline) and a bit line (Bitline), and the gate 304 is made of a material with resistive properties, such as HfOx. Among them, the gate 304 has three different states of insulation, high resistance and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com