BCH (Broadcast Channel) encoding and decoding method and device

An encoding method and encoding technology, which are applied in the field of BCH encoding and decoding methods and devices, can solve the problems of large delay in combinational logic, limiting the maximum frequency of encoders, and consuming too many XOR gates, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

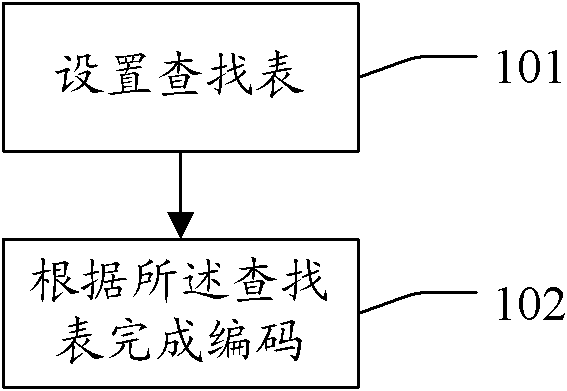

[0038] An embodiment of the present invention provides a BCH encoding method, such as figure 1 As shown, the BCH encoding method includes:

[0039] 101. A look-up table is set, and the coefficients of each level of the remainder polynomial are pre-stored in the look-up table, wherein the remainder polynomial is a bit-by-bit XOR operation between the high 8 bits of the current encoding status register and the current 8-bit encoding data, and the left The remainder of the polynomial pair generator polynomial obtained by shifting 104 bits;

[0040] 102. According to the current state of the encoding state register and the 8-bit data to be encoded, combined with the lookup table, obtain the state of the encoding state register at the next moment.

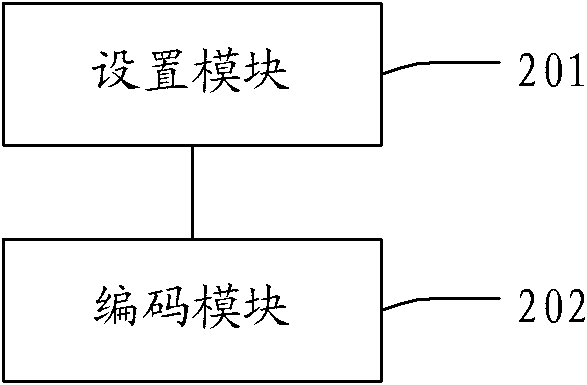

[0041] At the same time, the embodiment of the present invention also provides a BCH encoding device, including:

[0042] The setting module 201 is used to set the look-up table, and the coefficients of each level of the remainder pol...

Embodiment 2

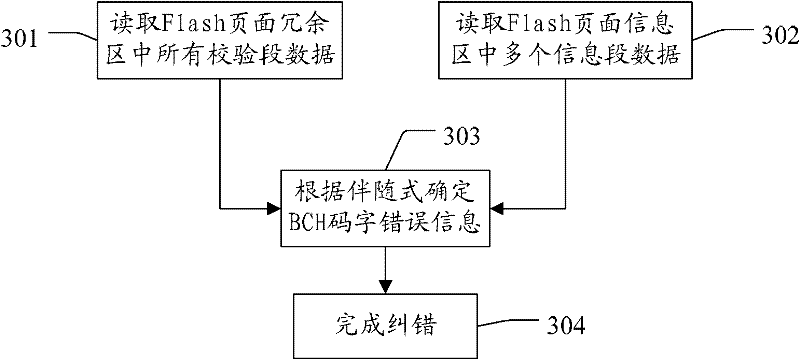

[0046] An embodiment of the present invention provides a BCH decoding method, such as image 3 As shown, the BCH decoding method includes:

[0047] 301. Read all the check segment data located in the page redundancy area in the flash memory, and store it in the data buffer;

[0048] 302. Read multiple information segment data in the page information area in the flash memory;

[0049] 303. Record the error information of each BCH code according to the accompanying formula corresponding to each information segment data, and store the error information in a data buffer;

[0050] 304. The system-on-chip data reader completes error correction according to the error information.

[0051] At the same time, the embodiment of the present invention also provides a BCH decoding device, such as Figure 4 shown, including:

[0052] The first reading module 401 is used to read all the parity segment data located in the redundant area of the page in the flash memory, and store it in th...

Embodiment 3

[0058] An embodiment of the present invention provides a BCH encoding method, such as Figure 5 As shown, the BCH encoding method includes:

[0059] 501. Set up a lookup table, the coefficients of each level of the remainder polynomial are pre-stored in the lookup table, wherein the remainder polynomial is a bit-by-bit XOR operation between the upper 8 bits of the current encoding status register and the current 8-bit encoding data, and the left The remainder of the polynomial pair generator polynomial obtained by shifting 104 bits;

[0060] The remainder polynomial is calculated as follows:

[0061] Let C(x) be any polynomial with the highest order of 103, namely:

[0062] C(x)=C 103 x 103 +C 102 x 102 +...+C 1 x+C 0 (1)

[0063] Then, C(x) can be expressed in either of the following two forms:

[0064] C ( x ) = x 96 C H ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com