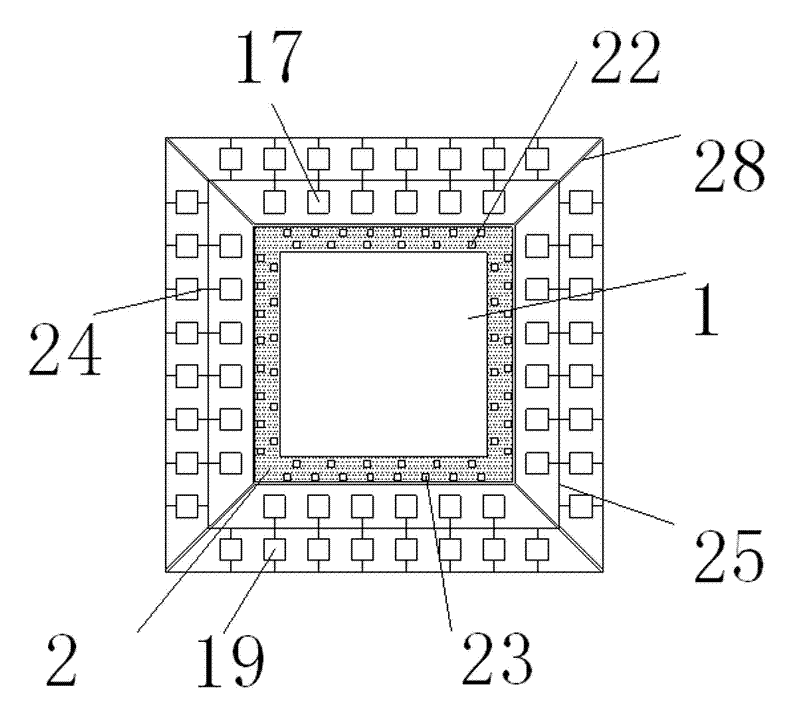

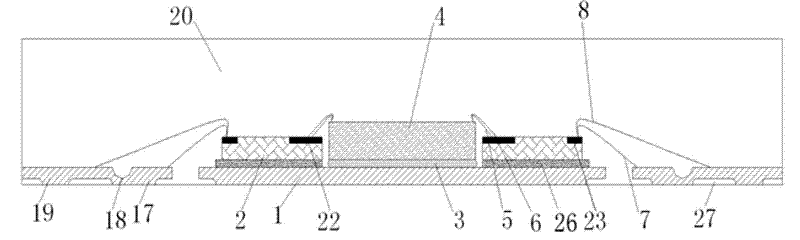

Center-wiring double-circle-arrangement single-IC (integrated circuit) chip packaging piece and preparation method thereof

A chip packaging and wiring technology, used in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve the problems of small number of pins, long bonding wires, and high bonding costs.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0035] Step 1 thinning and dicing

[0036] The wafer is thinned to 180μm and diced by conventional methods, and the dicing feed speed is controlled at ≤10mm / s;

[0037] Step 2 Core

[0038] Take the lead frame carrier, fix the IC chip 4 that has been thinned and diced in step 1 on the double-circle lead frame carrier 1, and bake for 3 hours with the anti-separation layer baking technology, the baking temperature is 150°C, and use ESPEC and other exhaust gases. Unobstructed, the temperature difference is less than ± 3 ℃ oven.

[0039] Step 3 Pressure Welding

[0040] First place the semi-finished lead frame transfer box with the center wiring ring 2 glued to the IC chip 4 on the feeding table of the pressure welding machine, then fix the gold wire or copper spool on the pressure welding table, and start the automatic loading of the pressure welding machine material device, the finished lead frame transfer box automatically rises to the set position, pushes out a semi-finishe...

Embodiment 2

[0050] Step 1 thinning and dicing

[0051] The wafer is thinned to 210μm and diced by conventional methods, and the dicing feed speed is controlled at ≤10mm / s;

[0052] Step 2 Core

[0053] Take the lead frame carrier, fix the IC chip 4 that has been thinned and diced in step 1 on the double-circle lead frame carrier 1, and bake for 3 hours with the anti-separation layer baking technology, the baking temperature is 150°C, and use ESPEC and other exhaust gases. Unobstructed, the temperature difference is less than ± 3 ℃ oven.

[0054] Step 3 Pressure Welding

[0055] First place the semi-finished lead frame transfer box with the center wiring ring 2 glued to the IC chip 4 on the feeding table of the pressure welding machine, then fix the gold wire or copper spool on the pressure welding table, and start the automatic loading of the pressure welding machine The finished lead frame transfer box automatically rises to the set position, pushes out a semi-finished lead frame to t...

Embodiment 3

[0065] Step 1 thinning and dicing

[0066] The wafer is thinned to 210μm and diced by conventional methods, and the dicing feed speed is controlled at ≤10mm / s;

[0067] Step 2 Core

[0068] Take the lead frame carrier, fix the IC chip 4 that has been thinned and diced in step 1 on the double-circle lead frame carrier 1, and bake for 3 hours with the anti-separation layer baking technology, the baking temperature is 150°C, and use ESPEC and other exhaust gases. Unobstructed, the temperature difference is less than ± 3 ℃ oven.

[0069] Step 3 Pressure Welding

[0070] First place the semi-finished lead frame transfer box with the center wiring ring 2 glued to the IC chip 4 on the feeding table of the pressure welding machine, then fix the gold wire or copper spool on the pressure welding table, and start the automatic loading of the pressure welding machine The finished lead frame transfer box automatically rises to the set position, pushes out a semi-finished lead frame to t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com