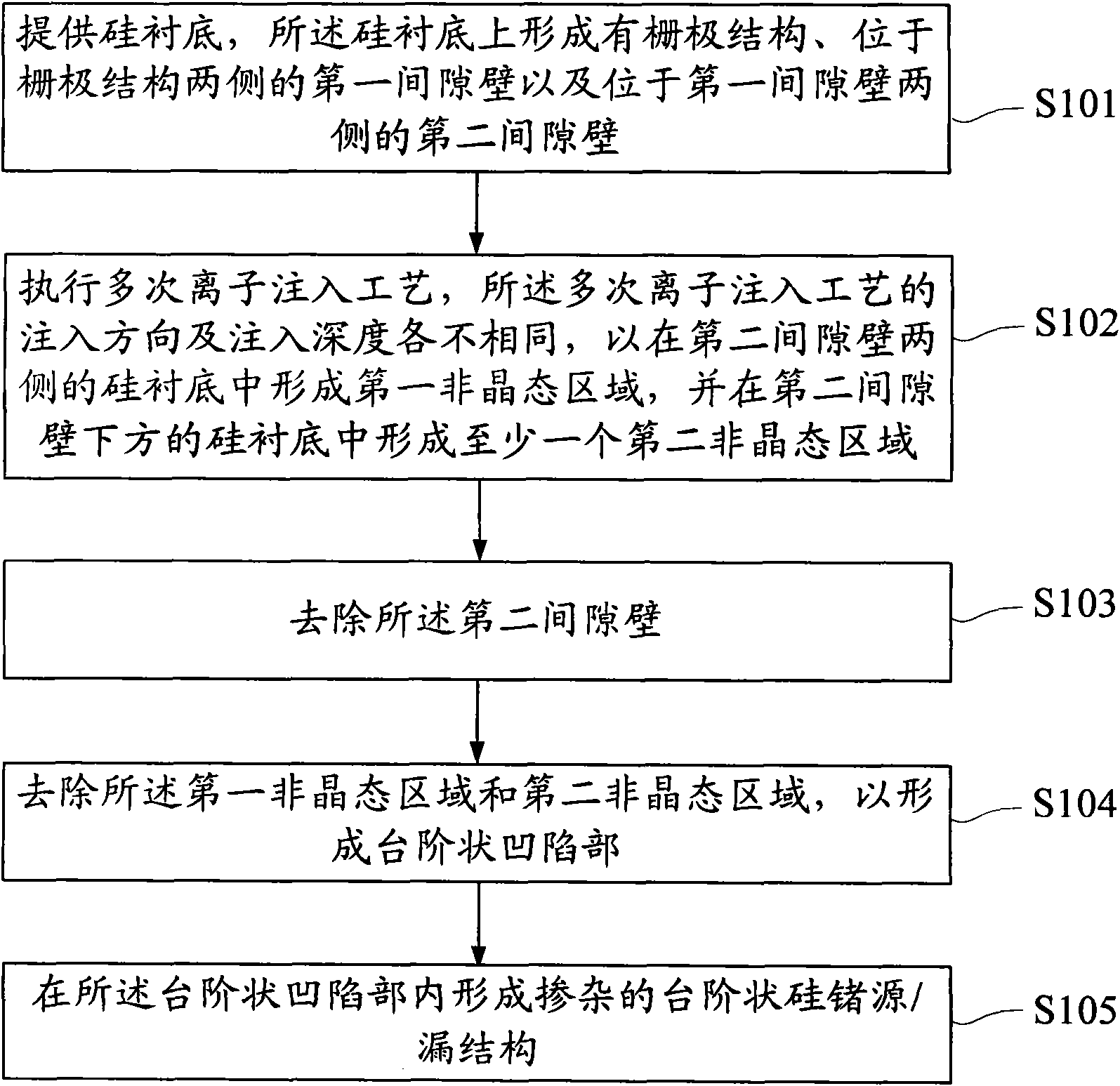

Manufacturing method for stepped silicon germanium source/drain structures

A manufacturing method and step-like technology, which are applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of poor etching selection, complex process steps, and difficult etching process control, and reduce etching steps. , The effect of high etching selection ratio and reducing control difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

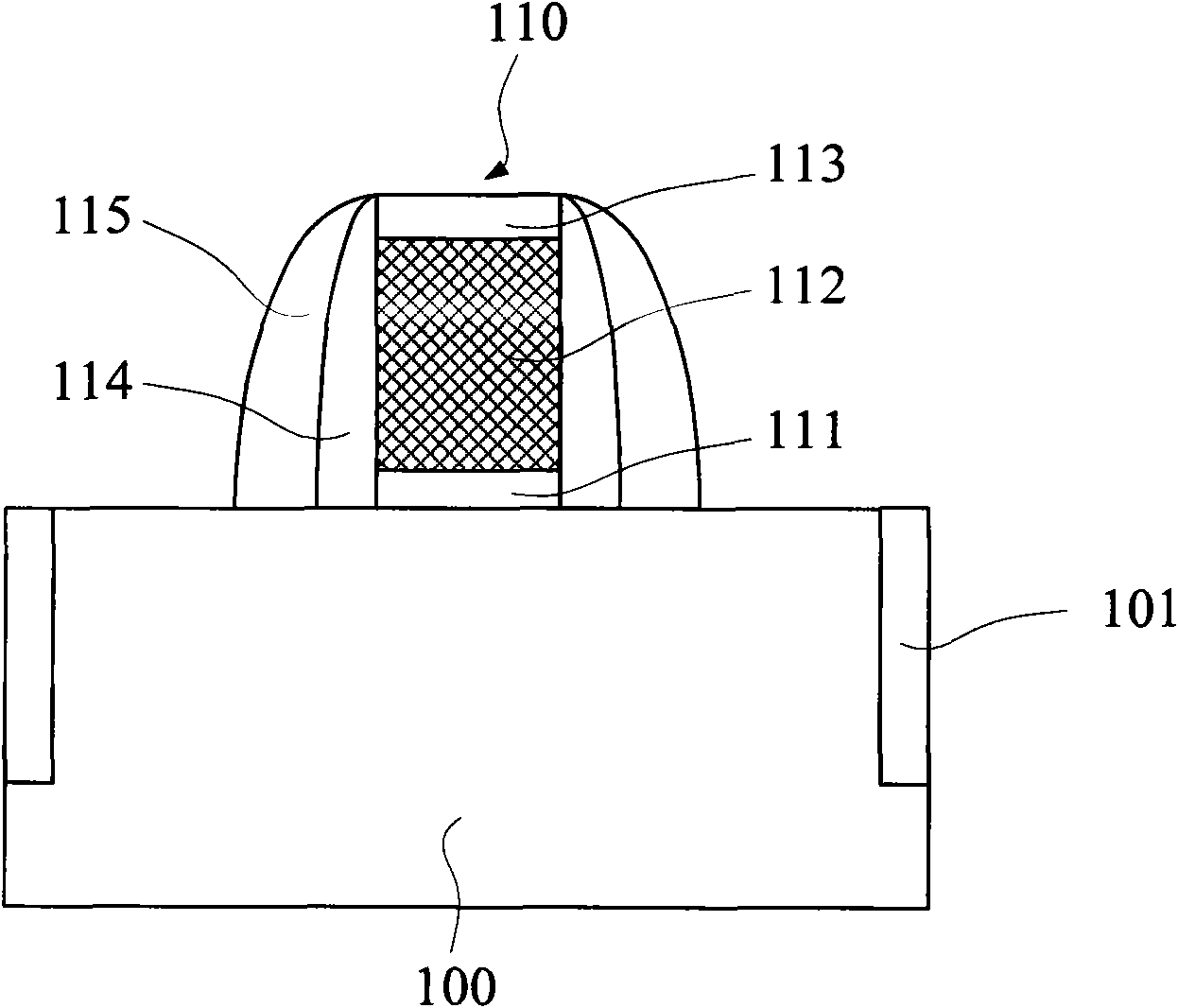

[0035] Such as Figure 2A As shown, and combined with step S101, first, a silicon substrate 100 is provided, and a gate structure 110 is formed on the silicon substrate 100, and then first spacers 114 are formed on both sides of the gate structure 110, and then Second spacers 115 are formed on both sides of the first spacer 114 .

[0036] Wherein, an isolation structure 101 may be formed in the silicon substrate 100, and the isolation structure 101 is, for example, a shallow trench isolation structure. The gate structure 110 includes a gate dielectric layer 111 and a gate electrode 112 covering the gate dielectric layer 111 . The material of the gate dielectric layer 111 may be silicon oxide, and the material of the gate electrode 112 may be doped polysilicon, metal, metal silicide or other conductors. Preferably, the gate structure 110 further includes a cover layer 113 covering the gate electrode 112, the material of the cover layer 113 can be one of silicon oxide or silic...

Embodiment 2

[0054] Such as Figure 3A As shown, a silicon substrate 200 is provided, and a gate structure 210 is formed on the silicon substrate 200, and then first spacers 214 are formed on both sides of the gate structure 210, and then on the first spacers 214 Second spacers 215 are formed on both sides, and an isolation structure 201 may be formed in the silicon substrate 200 .

[0055] The difference between this embodiment and Embodiment 1 is that in this embodiment, a total of three ion implantation processes are performed, wherein the angle between the implantation direction of the first ion implantation process and the surface of the silicon substrate 200 is a right angle, so that A first amorphous region is formed in the silicon substrate on both sides of the second spacer 215, and then a second ion implantation process and a third ion implantation process are performed, the second ion implantation process and the third ion implantation process The angle between the implantation...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com