Multi-finger strip-type gate-ground N-channel metal oxide semiconductor (GGNMOS) and electrostatic protection circuit

A strip-shaped, N-type technology, applied in the direction of circuits, electrical components, electric solid devices, etc., can solve the problems of poor conduction uniformity of GGNMOS parallel structure, parasitic NPN transistors cannot be simultaneously conducted, discharged, damaged, etc., to improve conduction The effect of uniformity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

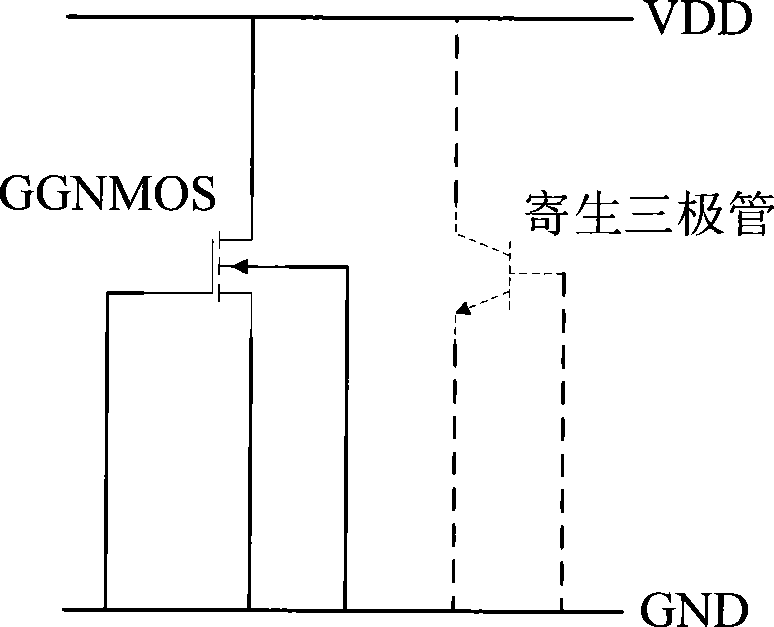

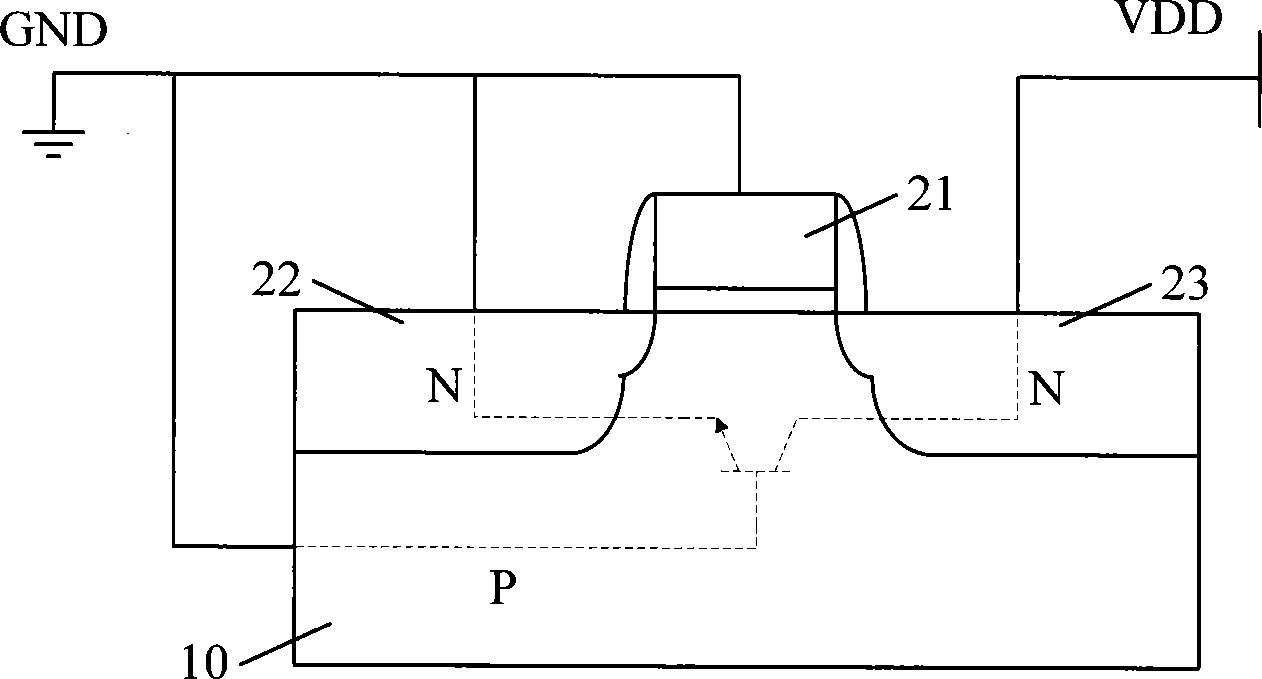

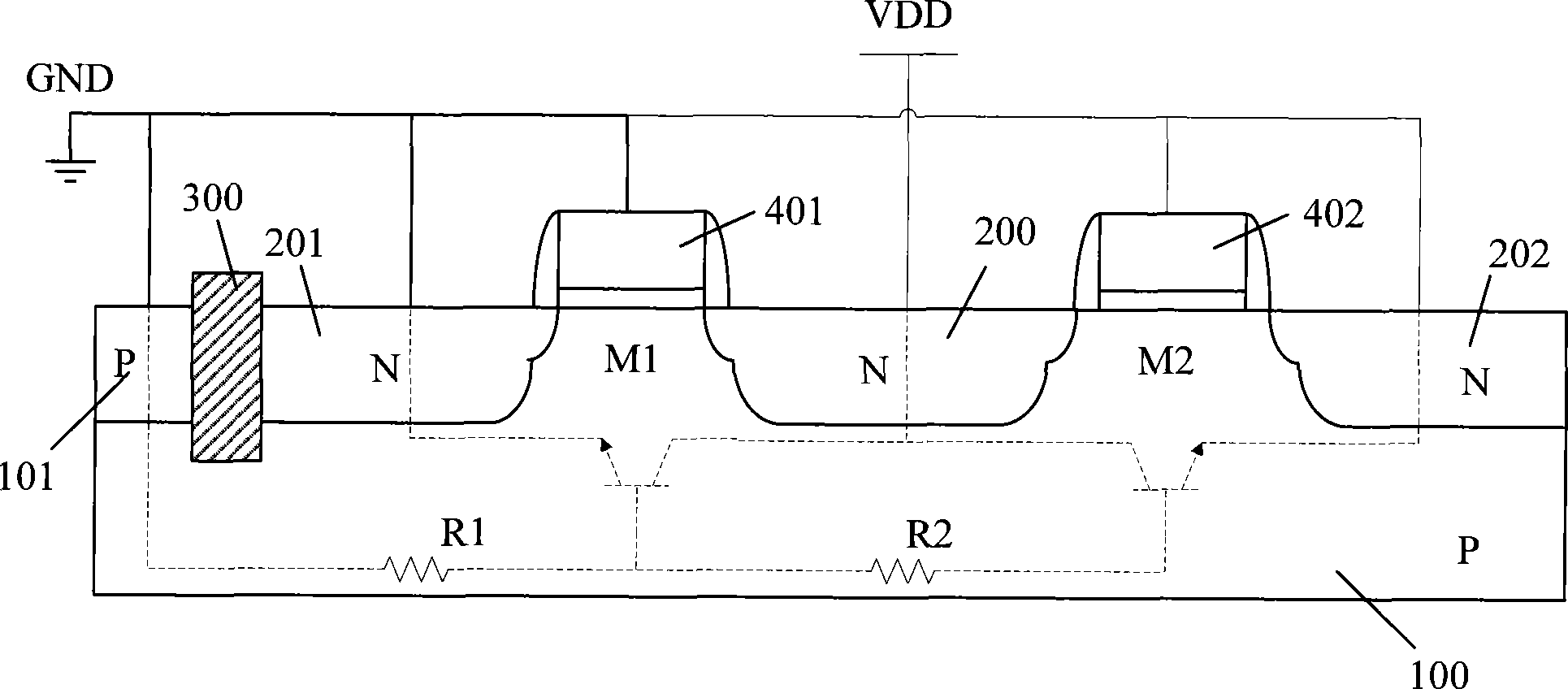

[0024] In the existing multi-finger strip GGNMOS, the parasitic internal resistance between the base and the ground of each parasitic NPN transistor is different, resulting in different base potentials of each parasitic NPN transistor, that is, the potential difference between the base and the emitter. The same, so the conduction uniformity is poor. When a voltage is applied to the drain, that is, the collector of the parasitic NPN transistor, each parasitic NPN transistor cannot be turned on at the same time, so part of the GGNMOS may be damaged. In the present invention, an N-type connection well is arranged between the drains of adjacent NMOS transistors in a multi-finger strip GGNMOS, thereby forming a parasitic internal resistance between the drain and an external circuit, and adjusting the N-type connection well surface area. The position of the N-type connection region can change the size of the parasitic internal resistance, thereby adjusting and improving the conductio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com