A Regression Test Management Method for Large Scale Integrated Circuits Based on Geometric Planning

A large-scale integrated circuit, regression testing technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of lack of test management methods, efficient testing, inability to effectively allocate computing resources, etc., to achieve optimal testing The effect of efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

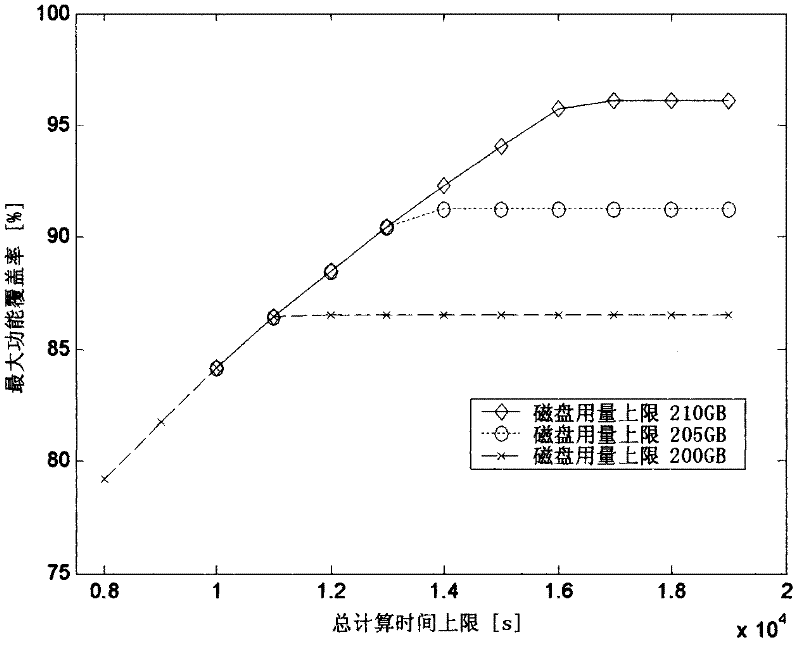

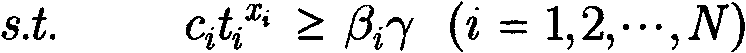

[0021] The following demonstrates the calculation process of the method for an RTL design containing 5 modules, each corresponding to 1 regression test.

[0022] 1) Obviously N=5, the parameter c obtained by fitting the functional coverage data i , x i For: (10.3, 0.31), (9.22, 0.29), (9.65, 0.27), (9.03, 0.28), (10.1, 0.26).

[0023] 2) Also run each regression test, collect disk usage information, and obtain its fitting parameter s i ,y i They are: (15.2, 0.15), (14.3, 0.12), (14.8, 0.14), (14.6, 0.11), (15.5, 013).

[0024] 3) A small amount of changes have been made to the RTL code. A set of weighted parameters βi provided by the designer are: 0.95, 0.95, 0.9, 0.9, 1, indicating that the changes are mainly concentrated on module 5, and the functional impact on module 1 and module 2 Larger, the impact on modules 3 and 4 is weaker.

[0025] 4) The administrator tries to provide an upper limit of available total computing time T=16000s and a total disk usage upper limit ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com