MEMS (micro electro mechanical system) wafer-level three-dimensional mixing integration packaging structure and method

A three-dimensional hybrid, integrated packaging technology, applied in microstructure technology, microstructure devices, manufacturing microstructure devices, etc., can solve the problem of high cost, and achieve the effect of reducing residual stress, simplifying process, and reducing manufacturing cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0049] In order to fully demonstrate the advantages and effects of the present invention, the substantive features and remarkable progress of the present invention will be further described below in conjunction with the accompanying drawings and embodiments, but the present invention is not limited by any means.

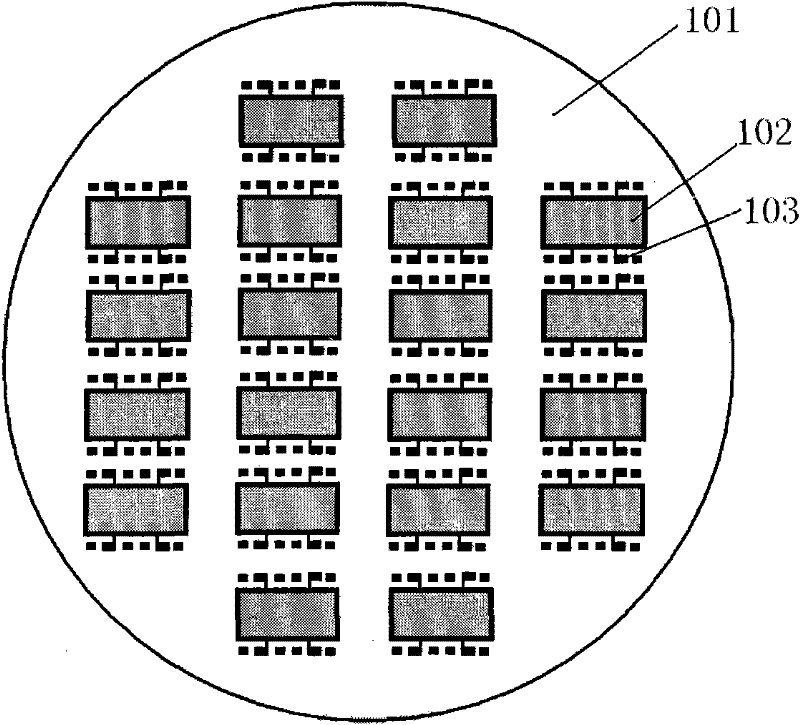

[0050] exist figure 1 Among them, on a silicon wafer 101, 102 is a MEMS device manufactured by MEMS technology, and Al metal leads and pads 103 are electrically connected to the MEMS device.

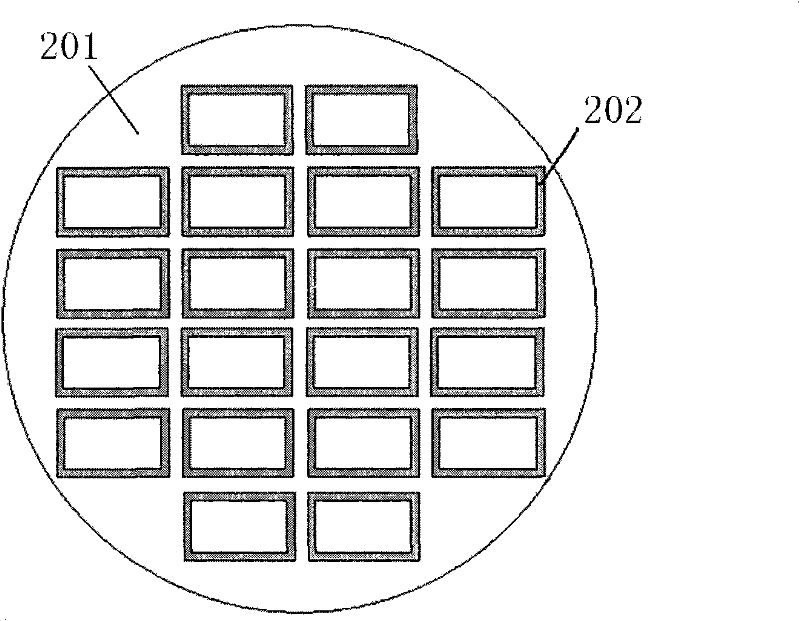

[0051] exist figure 2 Among them, the glass paste sealing ring 202 is printed on the silicon cover wafer 201 by screen printing. The seal ring 202 and the MEMS device 102 correspond to each other.

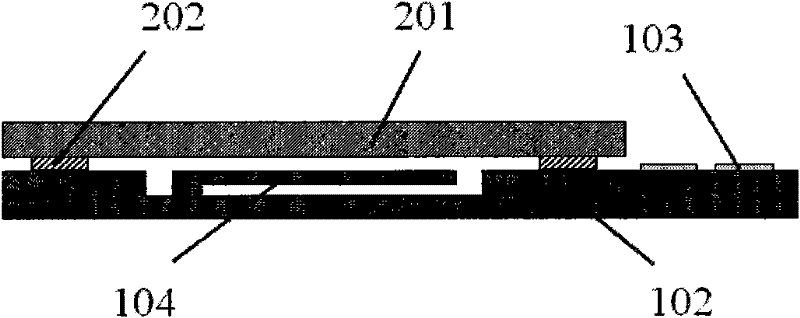

[0052] exist image 3 In the present invention, a silicon wafer 101 with MEMS devices is aligned and bonded to a silicon lid wafer 201 . The Al metal lead and the pad 103 pass through the bonding layer of glass paste to realize the electrical connection of the movable mechanism...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com