Method of manufacturing semiconductor device

A manufacturing method and semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve the problems of unable to prevent abnormal growth 13, unable to prevent the formation of oxides 12 or abnormal growth 13 and so on

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 2 example

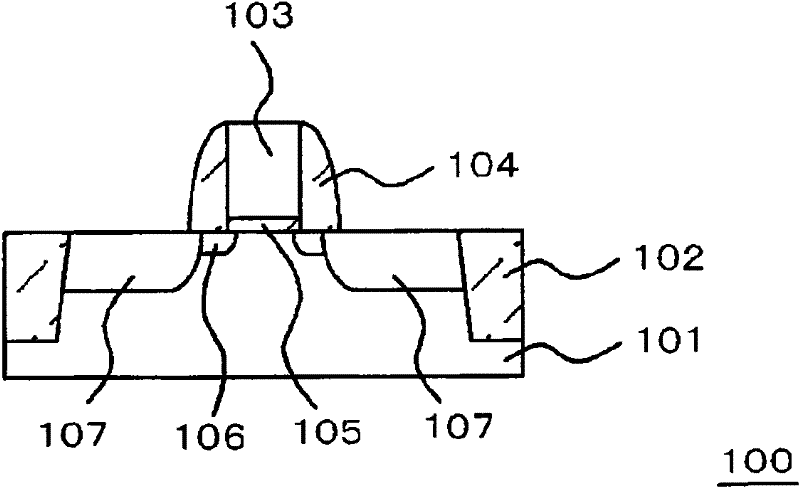

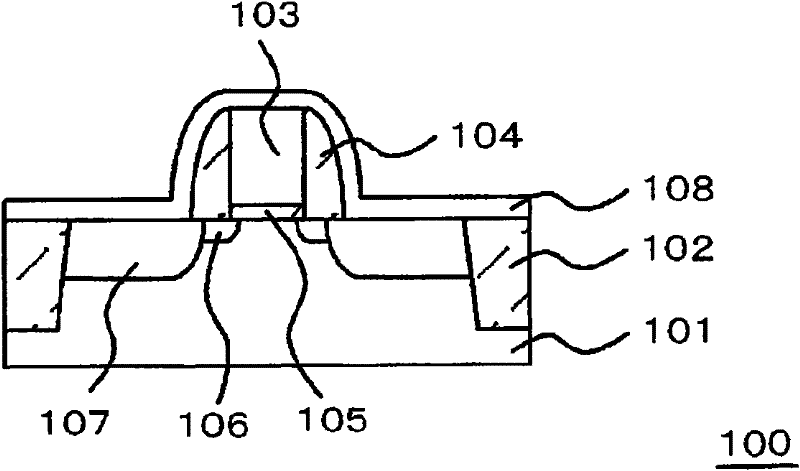

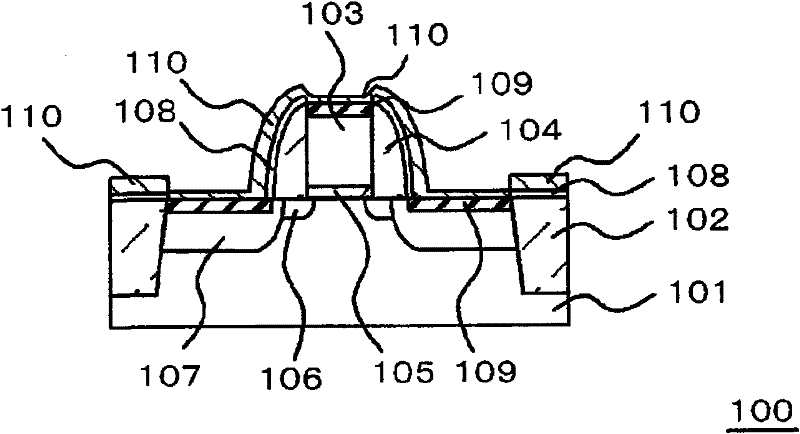

[0075] Figure 5A with 5B to Figure 7A with 7B is a process cross-sectional view showing an example of the manufacturing process of the semiconductor device 100 according to this embodiment.

[0076] First, using a well-known method, it is fabricated by forming STI 102 serving as an element isolation insulating film, gate electrode 103, side walls 104, gate insulating film 105, extension region 106, and source / drain region 107 on a silicon substrate 101. semiconductor components. Meanwhile, the source / drain regions 107 may be formed of materials such as SiGe and SiC. Next, a liner insulating film 120 and an interlayer insulating layer 122 are formed on the entire surface of the silicon substrate 101, and the insulating film is planarized by a chemical mechanical polishing (CMP) method ( Figure 5A ). In this embodiment, the gate electrode 103 may be formed of a metal material, for example.

[0077] Subsequently, using a photolithography technique and a reactive ion etc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com