Field programmable gate array (FPGA)-based integrated circuit chip testing system and method

A technology for integrated circuit and chip testing, applied in the direction of digital circuit testing, electronic circuit testing, electrical measurement, etc., can solve the problems of strict cost control of chip testing, short design cycle, large shipment volume, etc., and achieve fast testing speed. , low cost and stable performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

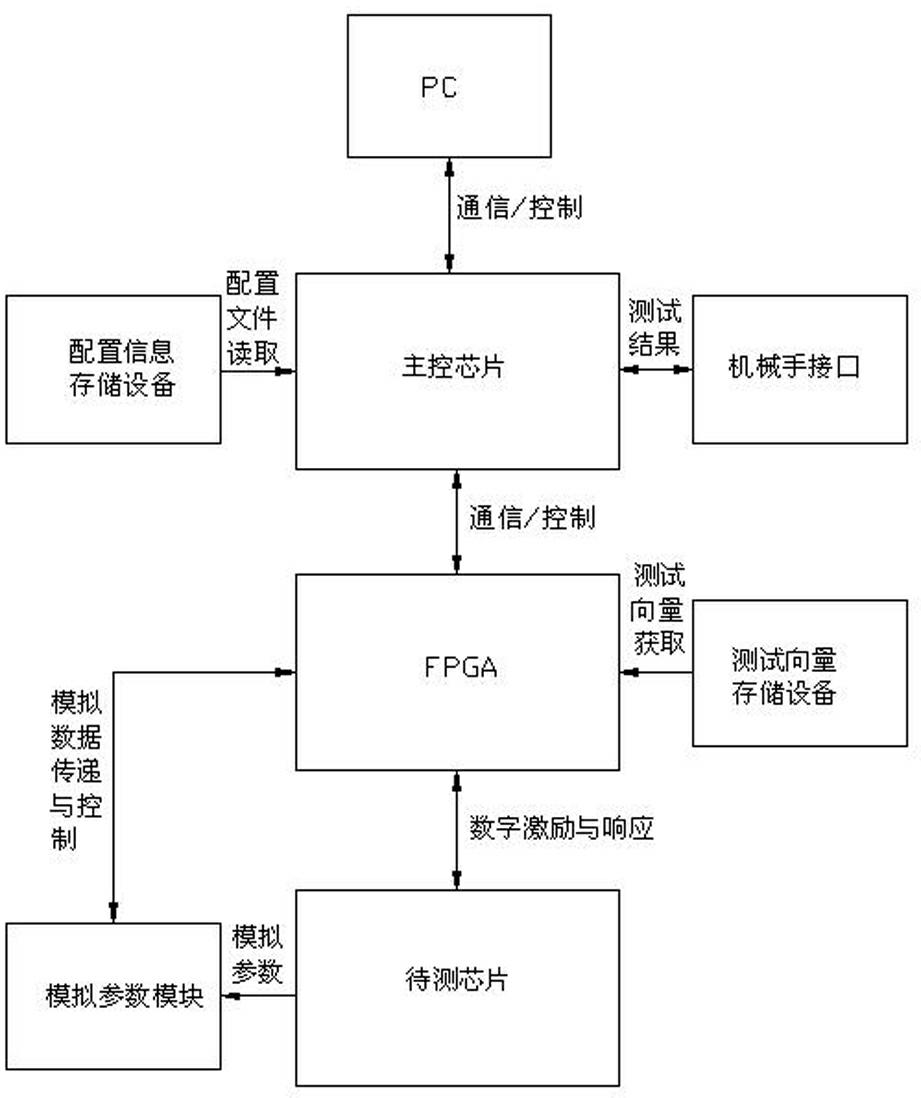

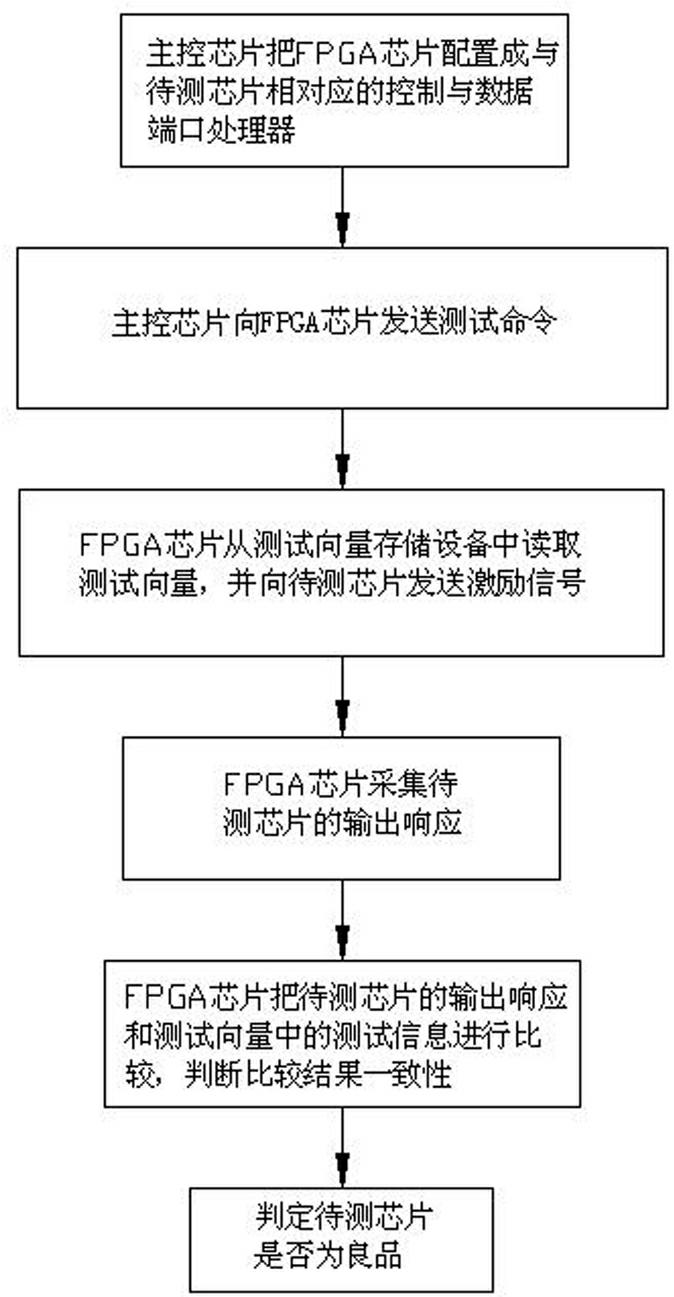

[0046] Such as figure 1 , figure 2 As shown, the present invention relates to an FPGA-based integrated circuit chip testing system and a method for testing integrated circuit chips with digital modules using the testing system. In this embodiment, the test system includes a PC, a main control chip, an FPGA chip, a configuration information storage device, a test vector storage device and a manipulator interface. The test vector storage device can be a U disk, SD card or MS card. Such as Figure 4As shown, the FPGA chip includes a CPU, a clock generator, a test vector memory, a timer, a removable storage interface, and a serial data interface. Between the PC and the main control chip, between the main control chip and the FPGA chip, between the main control chip and the configuration information storage device, between the PFGA chip and the test vector Connections are realized between the storage devices and between the FPGA chip and the chip to be tested. The manipulator...

Embodiment 2

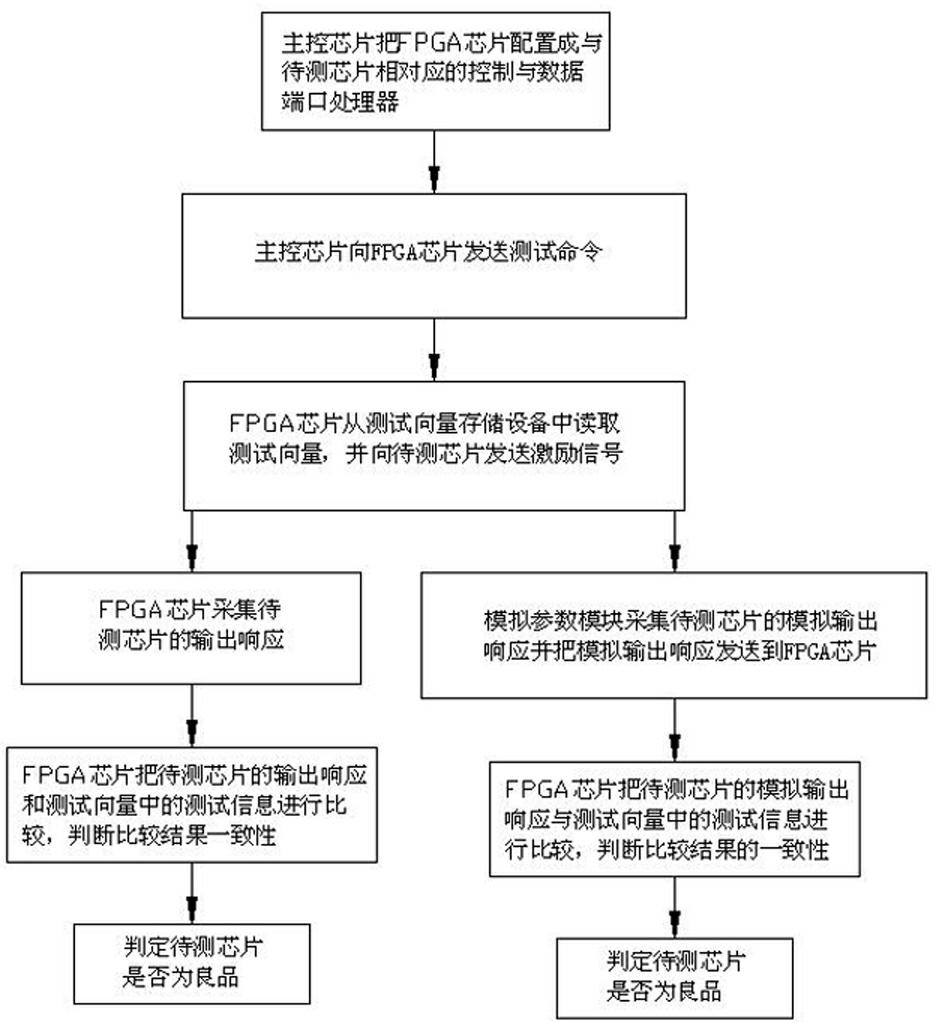

[0058] The difference between this embodiment and Embodiment 1 is that: in addition to including digital modules, the chip to be tested also includes analog modules, and accordingly, the FPGA-based integrated circuit chip test system also includes analog parameters. module, the analog parameter module is used to test the analog parameter value of the chip to be tested, and transmit the test value to the FPGA chip. In the present embodiment, the test steps when using the FPGA-based integrated circuit chip test system to test the chip to be tested are as follows:

[0059] (a) The main control chip configures the FPGA chip with the configuration information stored in the configuration information storage device, and configures it as a control and data port processor corresponding to the chip to be tested;

[0060] (b) The main control chip sends a test command to the FPGA chip;

[0061] (c) After the FPGA chip receives the test command, it reads the test vector from the test vec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com