Emission microscope chip failure analyzing method and system

A low-light microscope and failure analysis technology, applied in the field of low-light microscope chip failure analysis methods and systems, to reduce complexity, facilitate stable insertion and removal, and improve analysis efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

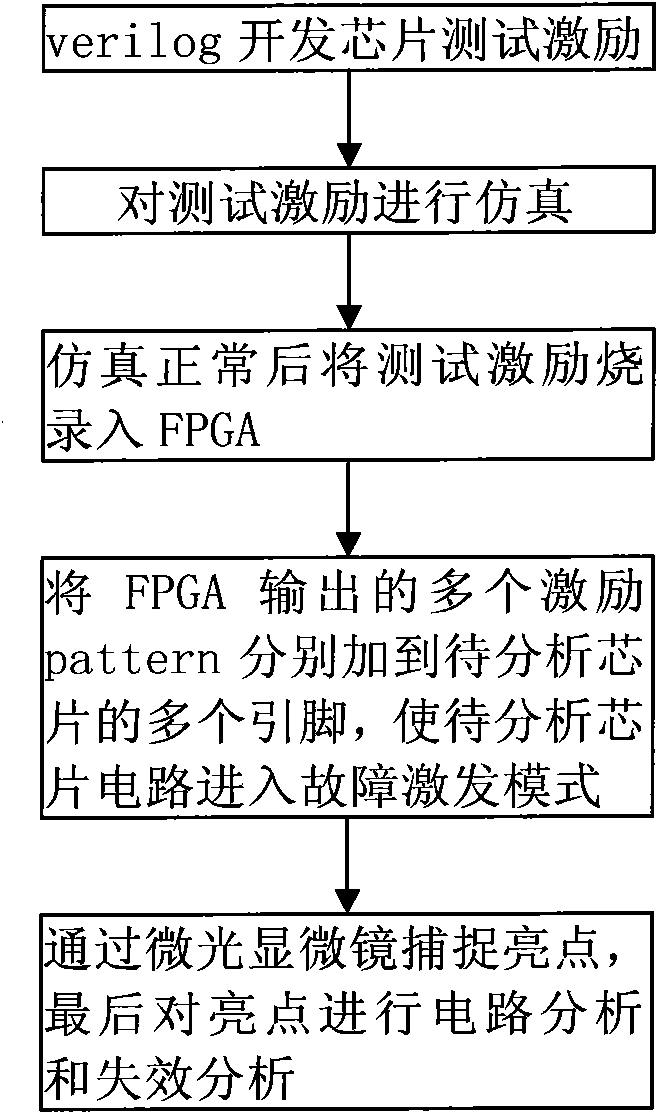

[0031] An embodiment of the micro-light microscope chip failure analysis method of the present invention is as follows: figure 1 shown, including the following steps:

[0032] 1. Using the hardware description language verilog to develop chip test incentives;

[0033] Two. use Quatus software to simulate the test stimulus, after the simulation is normal, the test stimulus is burned into the FPGA (Field Programmable Gate Array, Field Programmable Gate Array) substrate;

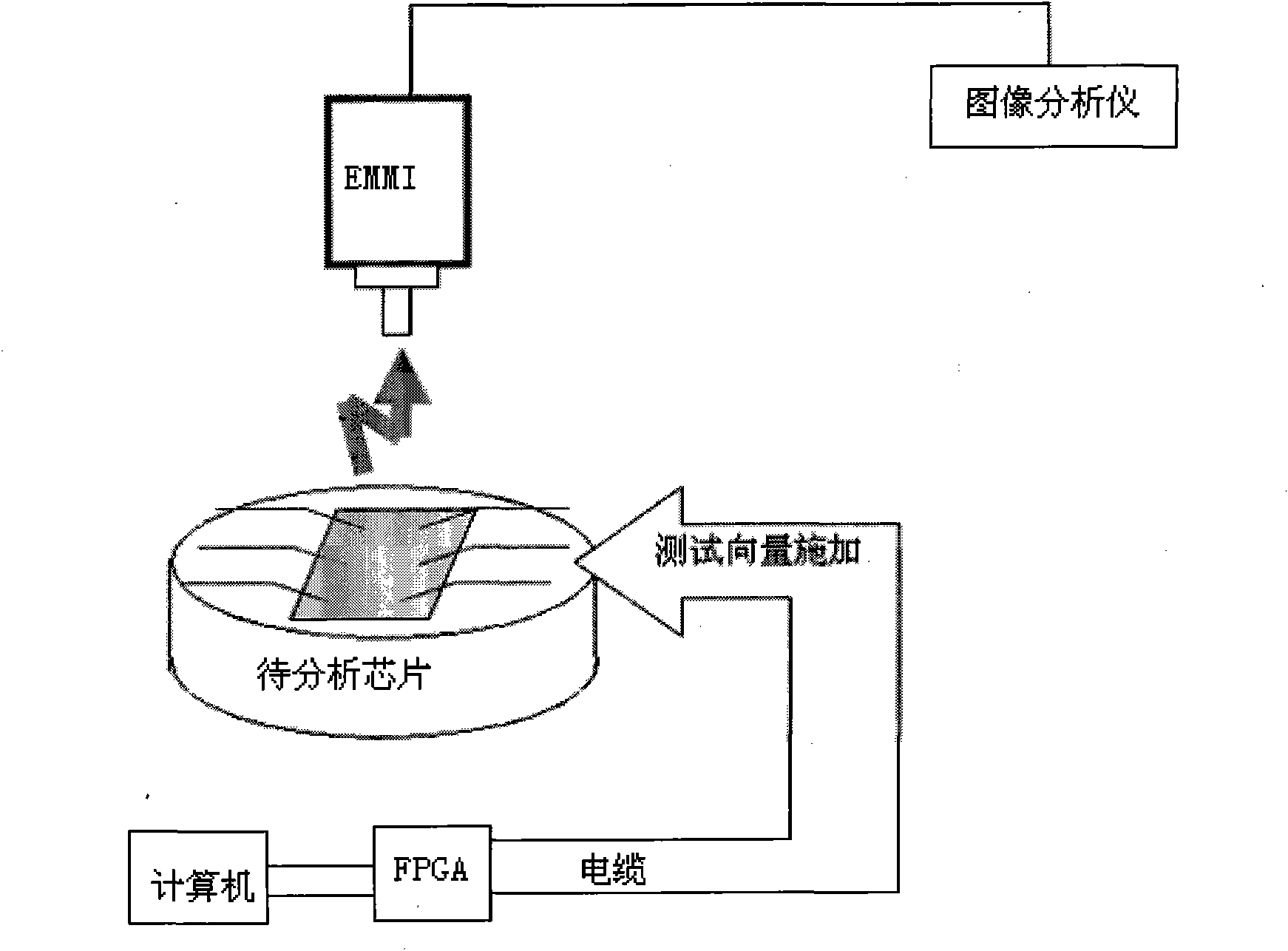

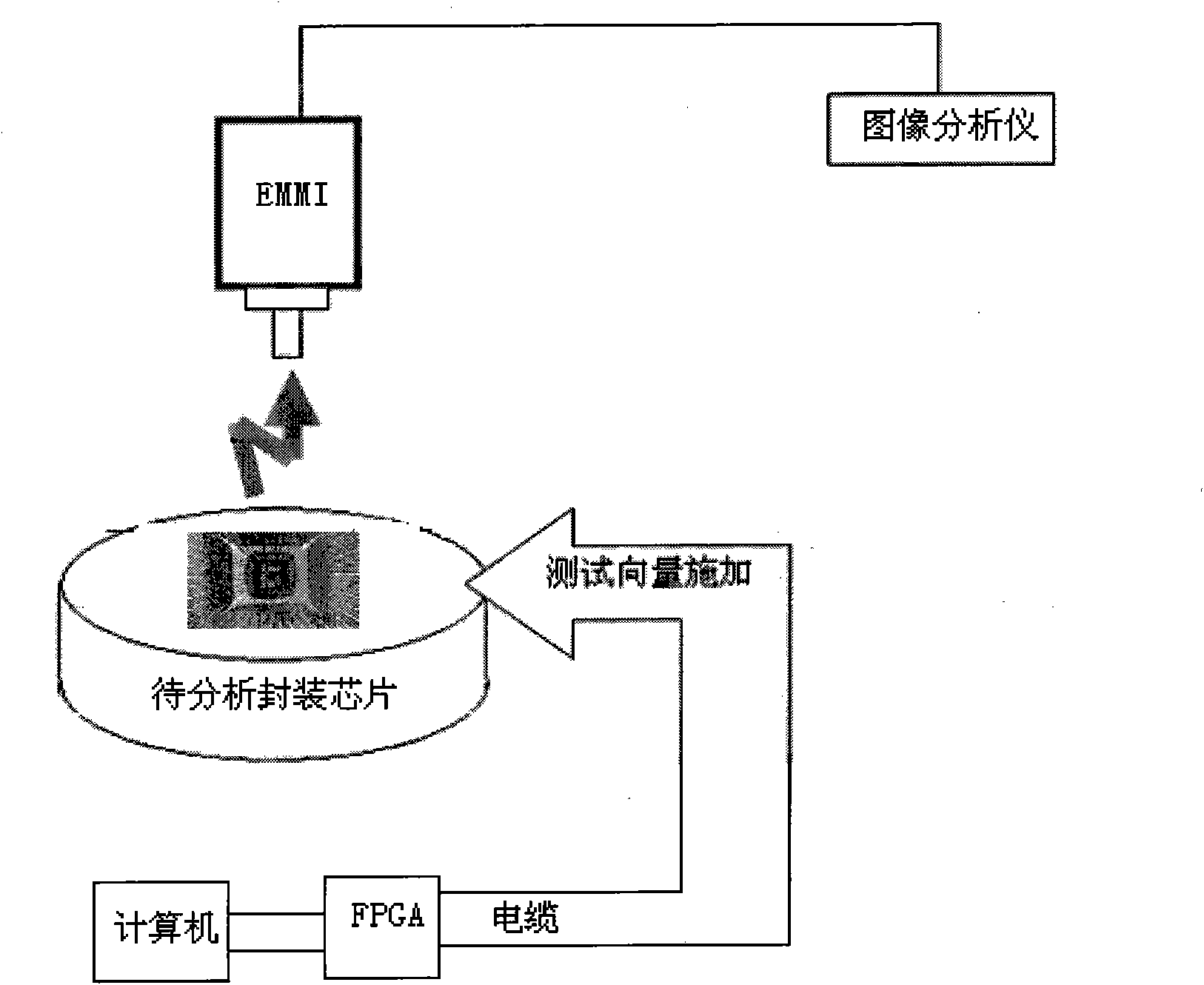

[0034] 3. The FPGA substrate has a plurality of excitation pattern outputs, and the plurality of excitation pattern outputs are respectively connected to a plurality of pins of the chip to be analyzed through cables, so that a plurality of excitation patterns are respectively added to a plurality of pins of the chip to be analyzed, Make the chip circuit to be analyzed enter the fault excitation mode;

[0035] 4. Capture the bright spots through the micro-light microscope (EMMI), and finally conduct circuit an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com