Quasi-cyclic low density parity-check code (QC-LDPC) decoder and decoding method

A low-density parity and decoder technology, applied in the field of solid-state hard disk error correction systems, can solve the problems of wasting clock cycles, low bit error rate, and complex implementation, and achieve the effect of reducing chip area, optimizing system performance, and improving efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

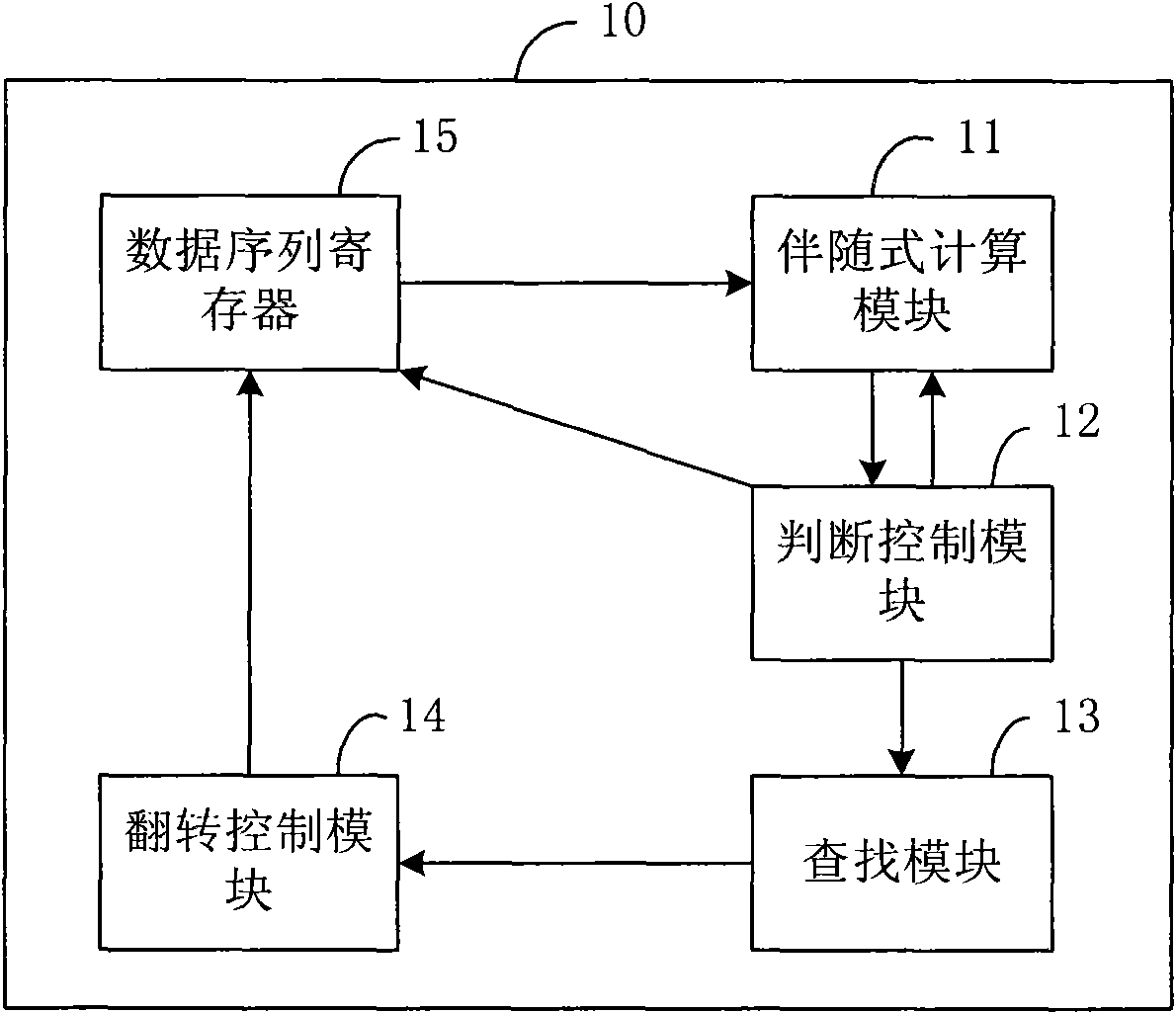

[0040] Such as figure 1 As shown, a quasi-cyclic low-density parity-check code (QC-LDPC) decoder 10 of the present invention is applied to a solid state disk error correction system 100 and uses Bit Flipping for decoding. The decoder 10 includes a syndrome calculation module 11 , a judgment control module 12 , a lookup module 13 , an inversion control module 14 , a data sequence register 15 and an iteration number judgment module 16 .

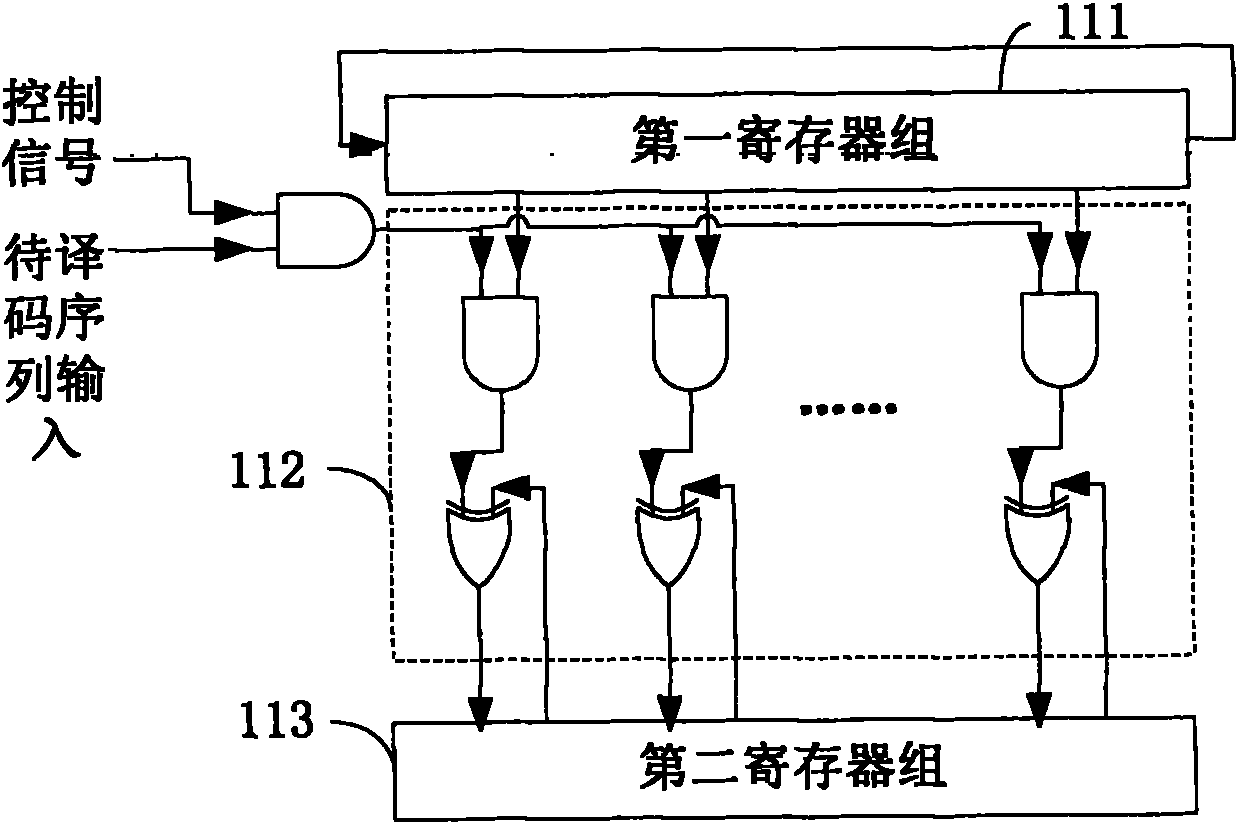

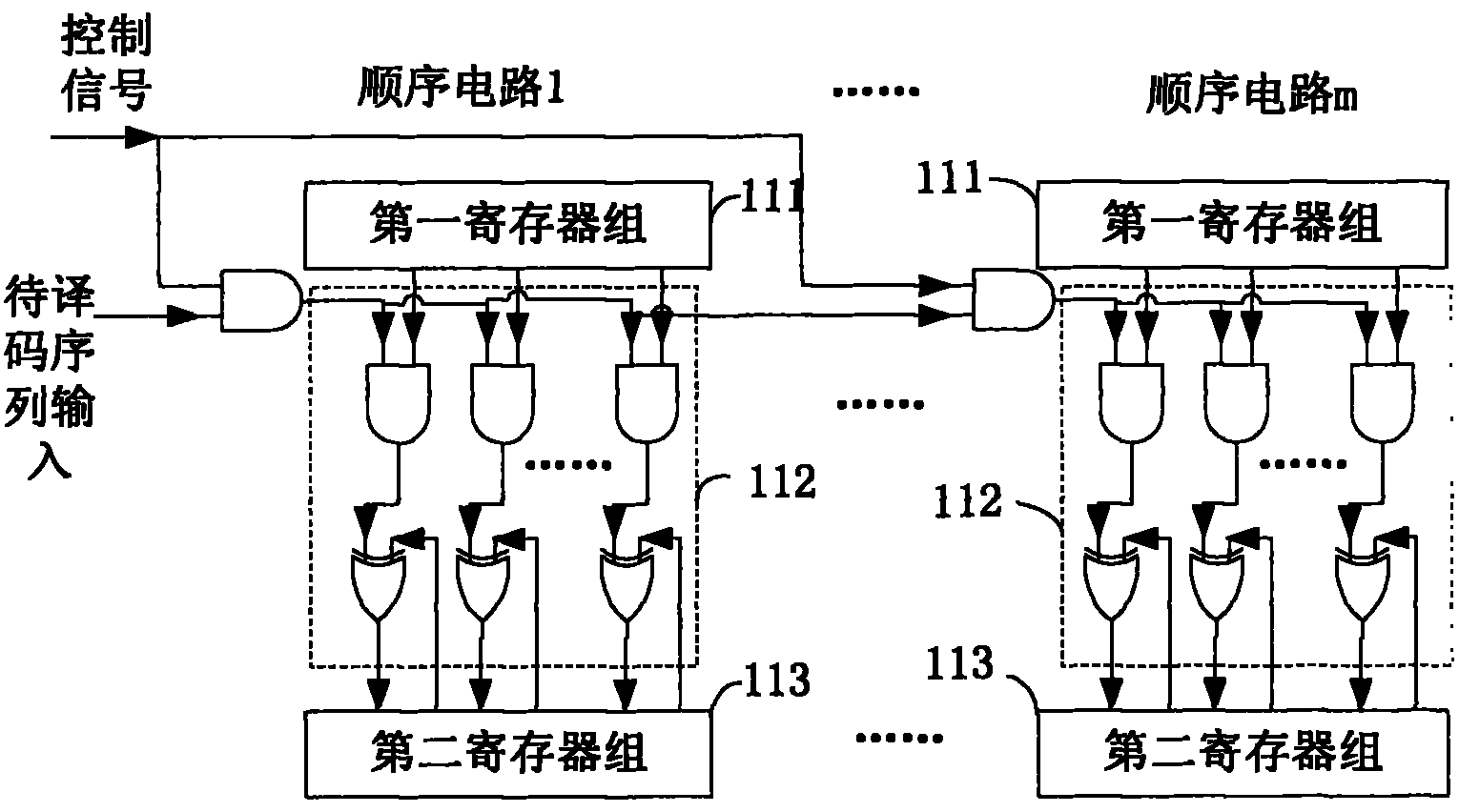

[0041] Syndrome calculation module 11, configured to calculate the syndrome of the sequence to be decoded. The circuit structure of the accompanying formula calcu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com