Groove type power MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) and manufacturing method thereof

A manufacturing method and trench technology, applied in semiconductor/solid-state device manufacturing, electrical components, transistors, etc., can solve problems such as increasing gate turn-on voltage, reduce gate-drain capacitance, and improve switching speed.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0053] Such as Figure 3 to Figure 14 Shown, the present invention manufactures trench type power MOSFET and comprises the following process steps:

[0054] Step 1: Reference image 3 , Figure 4 , using an N+ type substrate doped with As, growing a 5-10um epitaxial layer 2 on the substrate, the preferred thickness of the epitaxial layer 2 is 3-3.5um, and using a thermal oxidation process on the epitaxial layer 2 Depositing a third oxide layer 3 of 6000A;

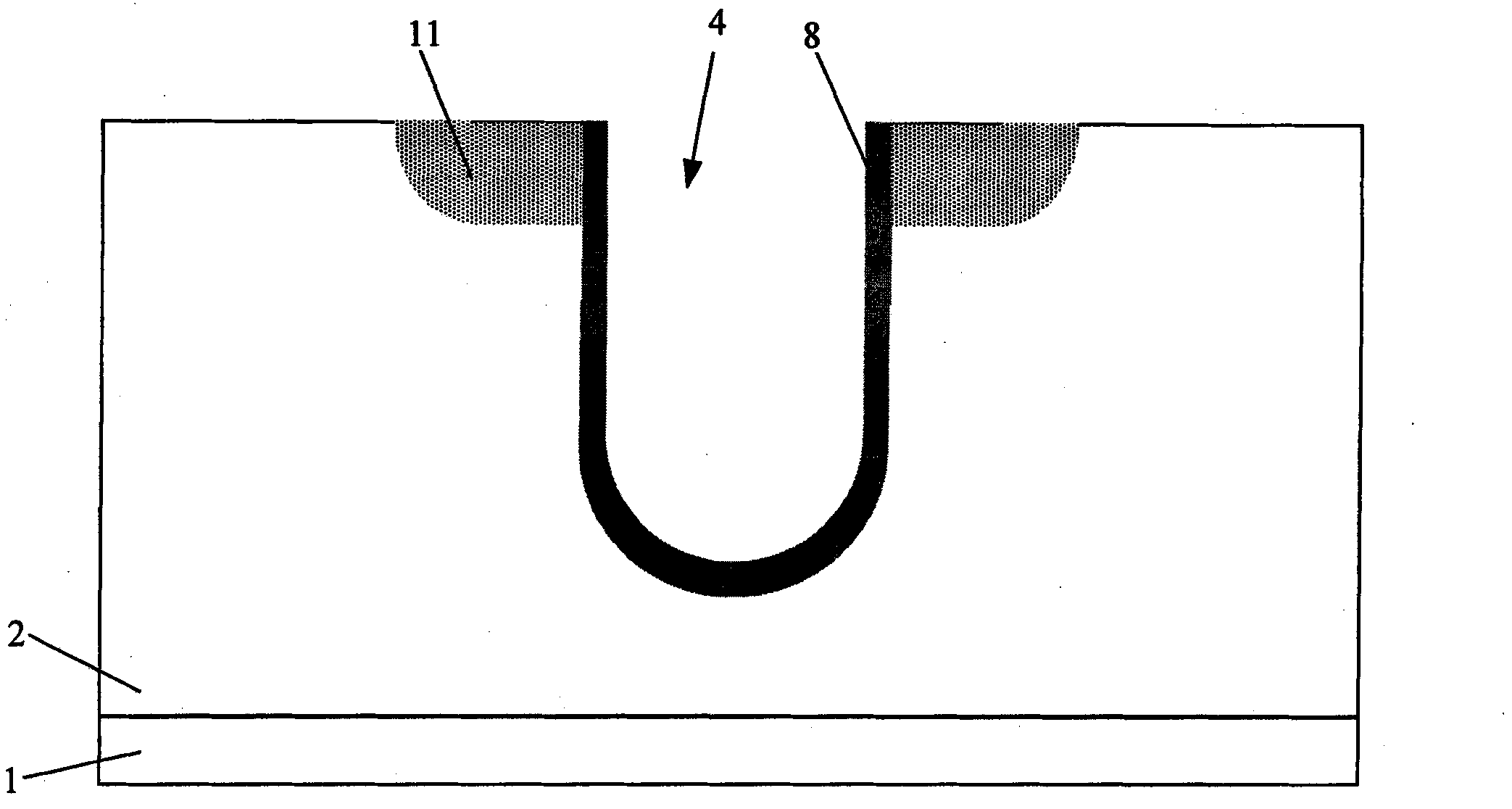

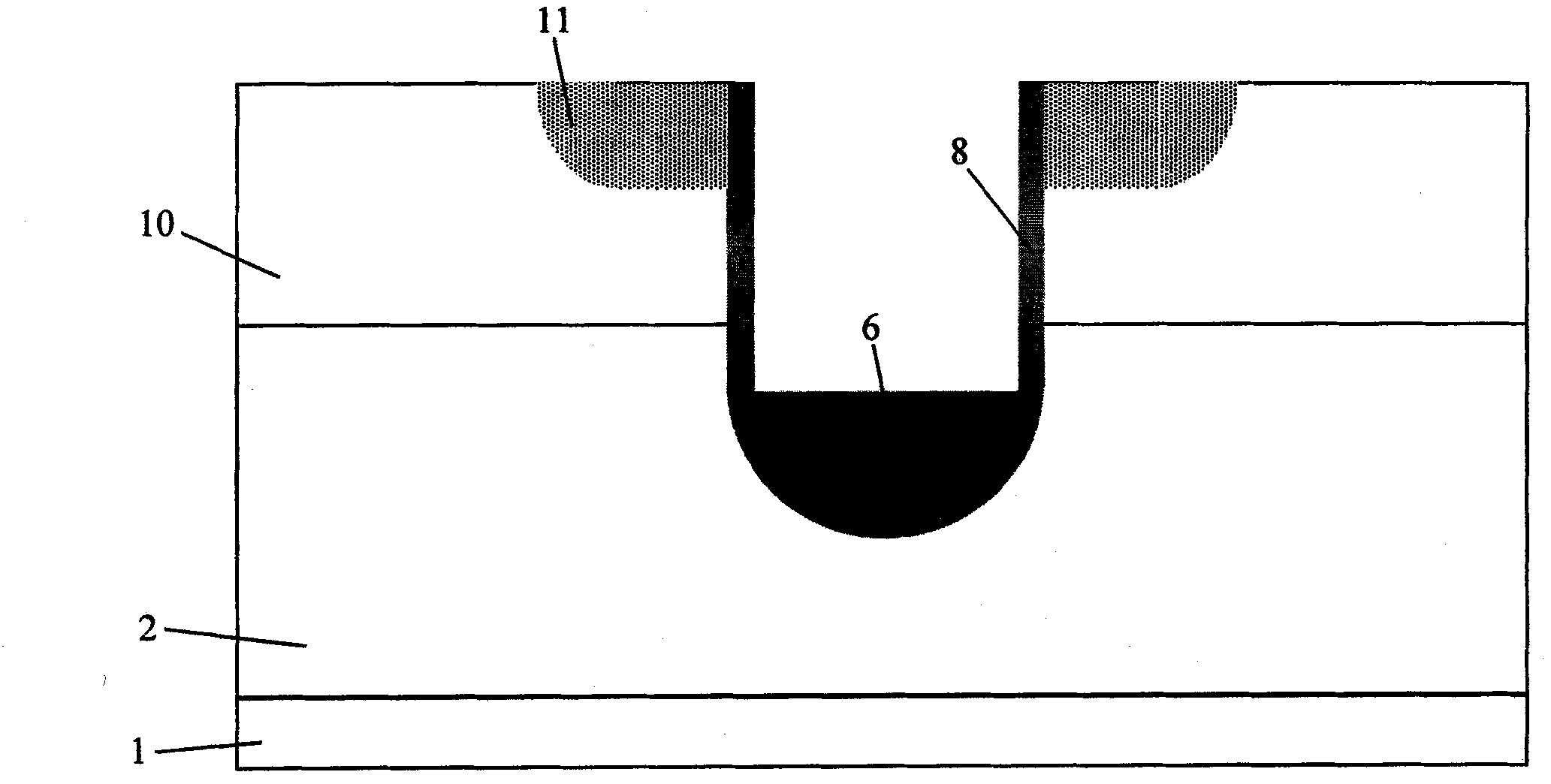

[0055] Step 2: Reference Figure 4-Figure 9 , etch a trench 4 with a width of 0.4-0.6um and a depth of 1um-1.6um and form a thickened oxide layer 6 with a thickness of 0.15-0.25um in the trench 4, wherein the thickened oxide layer is formed Step 6 also includes:

[0056] Step 20: Deposit a second oxide layer 5 in the trench until the trench 4 is completely filled. For details, refer to Figure 4 , Figure 5 and Figure 6 , coat 2um photoresist 3a on the third oxide layer 3, form trench etching window 3b after exposu...

Embodiment 2

[0067] Such as Figure 3 to Figure 18 As shown, another embodiment of the present invention manufactures the trench power MOSFET and comprises the following process steps:

[0068] Steps 1-5 of the method in the second embodiment are the same as those in the first embodiment, except that the following steps are also included.

[0069] Step 6: Reference Figure 15 , Figure 16 , deposit a first oxide layer 12 with a thickness of 1.6-1.7um, and grind the first oxide layer 12 by chemical mechanical polishing, and the thickness of the first oxide layer 12 after grinding is 6000-8000A, and then contact Hole photolithography is used to carve a contact hole window 13, and a grooved contact hole 14 is formed through the contact hole window 13 using a plasma etching process, and the grooved contact hole 14 passes through the first oxide layer 12, the source region 11 and is connected with The P well region 10 is contacted, and the groove contact hole 14 has a width of 0.3-0.4um and ...

Embodiment 3

[0085] Embodiment 2 uses a P-type semiconductor, its principle is the same as Embodiment 1 and Embodiment 2, and the process steps are also the same as Embodiment 1. The difference is that the substrate it uses is a P-type substrate, on which the substrate grows The epitaxial layer is a P-type epitaxial layer, the well above the epitaxial layer is an N-well region, the source region above the N-well region is a P+-type source region, and there is P+-doped polysilicon in the trench. The implanted region is an N+ implanted region, and the rest of the oxide layer and the filling metal in the trench contact hole are the same as those in Embodiment 1 and Embodiment 2.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com