PCB encapsulation of surface patch capacitor, method thereof, PCB and equipment

A printed circuit board and surface mount technology, which is applied in the direction of assembling printed circuits with electrical components, printed circuits connected with non-printed electrical components, and the formation of electrical connections of printed components, can solve the problem of increased capacitance distribution, inductance, and capacitance filtering Effect reduction and other issues, to achieve the effect of reducing distributed inductance, improving effect, and saving design workload

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

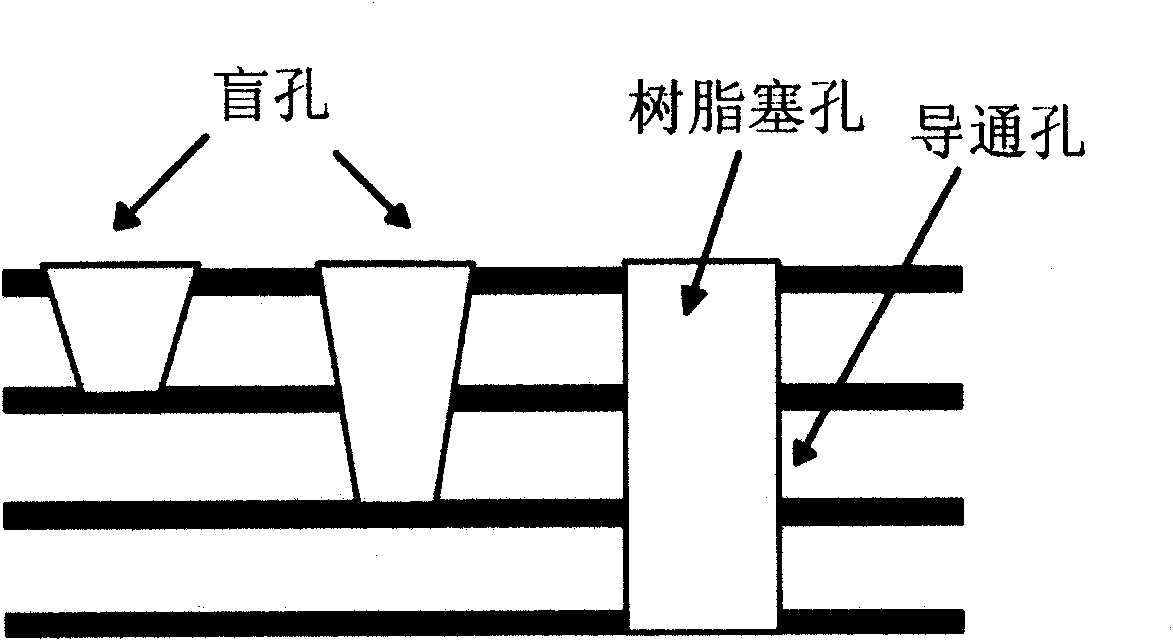

Method used

Image

Examples

Embodiment 1

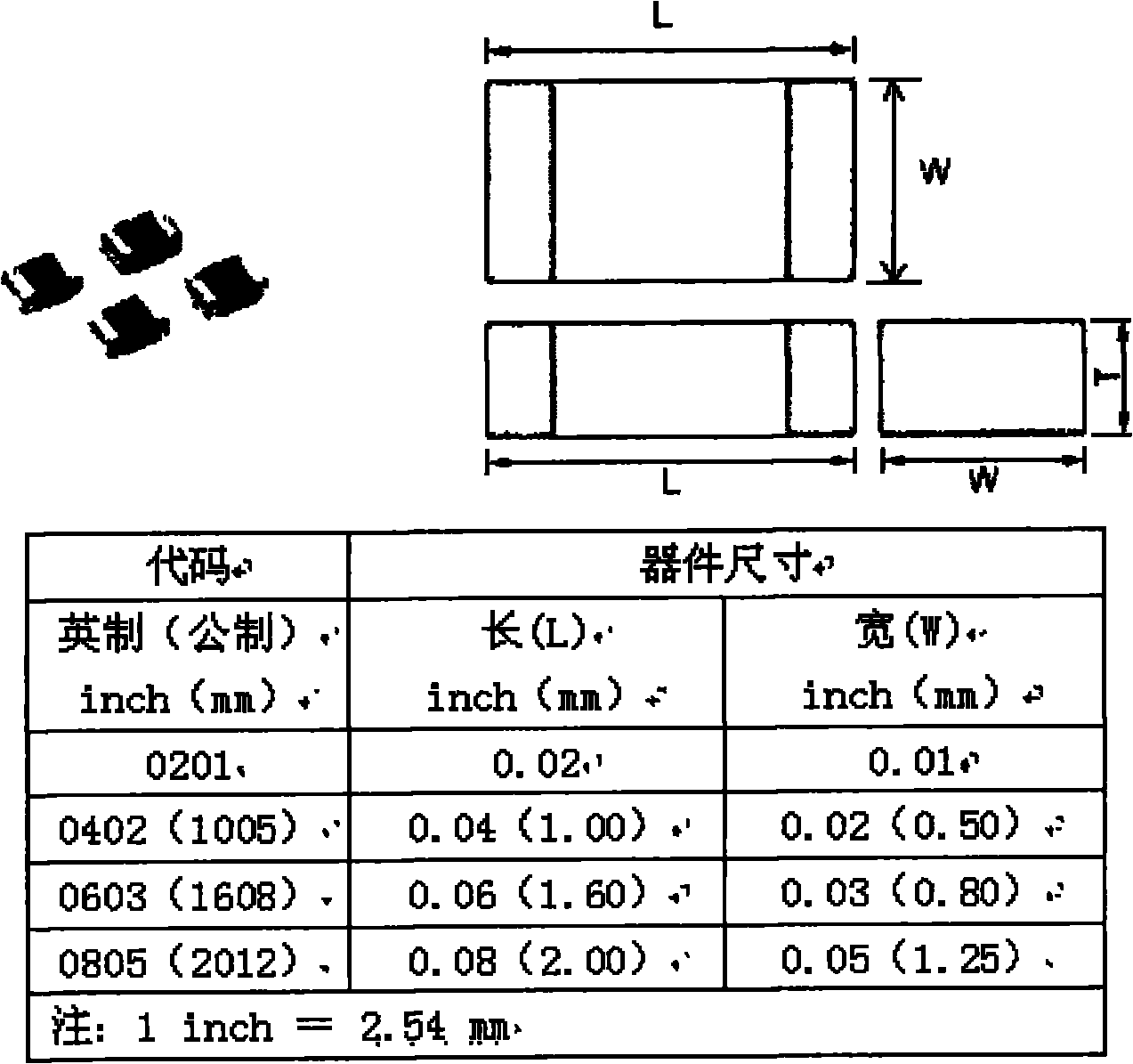

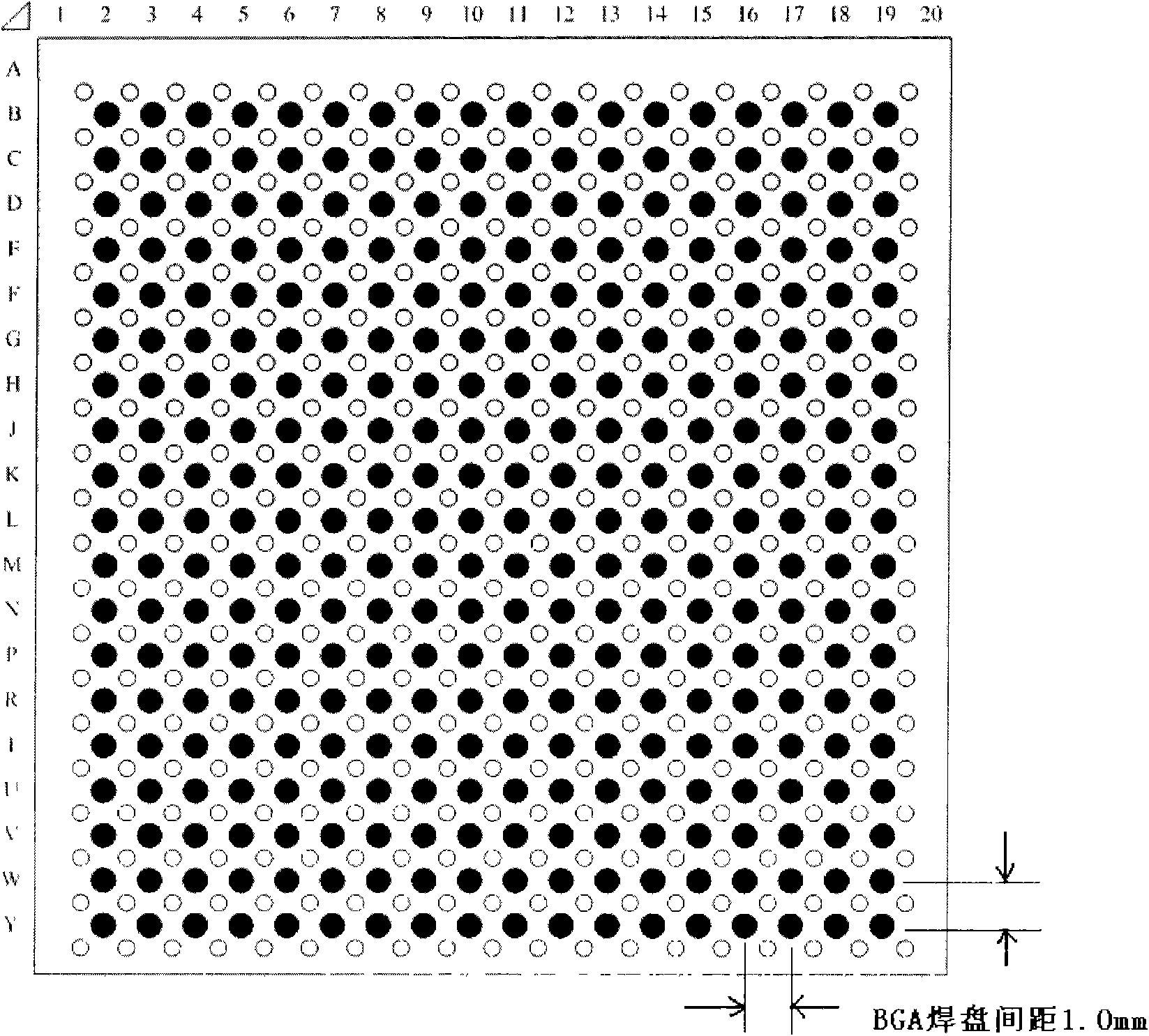

[0051] Preferred embodiment one: take 0402 SMT electric capacity, the pad pitch of BGA chip is 1.0mm as example, the PCB encapsulation method of SMT electric capacity of the present invention mainly comprises the following steps:

[0052] Step 1, create a new 0402 PCB package design: adjust the value of the standard 0402 pad to get a package with new pad width, pad length and two pad spacing values, so that on the pad Add vias. If the via hole adopts laser blind hole or mechanical via hole with an outer diameter of 18mil, it is not necessary to adjust the standard PCB package size of 0402; if the PCB board is thick, a mechanical via with an outer diameter of ≥20mil is required. For through holes, the width, length and spacing of the two pads need to be adjusted accordingly.

[0053] Step 2, add a via hole on each of the two pads of the capacitor, and adjust the position of the via hole according to the PCB package size of 0402 and the BGA pad spacing of 1.0mm. The via hole c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com