Method for enhancing pressure resistance capacity of chip in packaging process and chip thereof

A technology for compressive strength and chip enhancement, which is applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid state devices, etc. It can solve problems such as poor compressive capacity, collapse of insulating dielectric layers, scrapped chips, etc., to improve reliability, The effect of preventing capacitance and enhancing the ability to resist pressure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

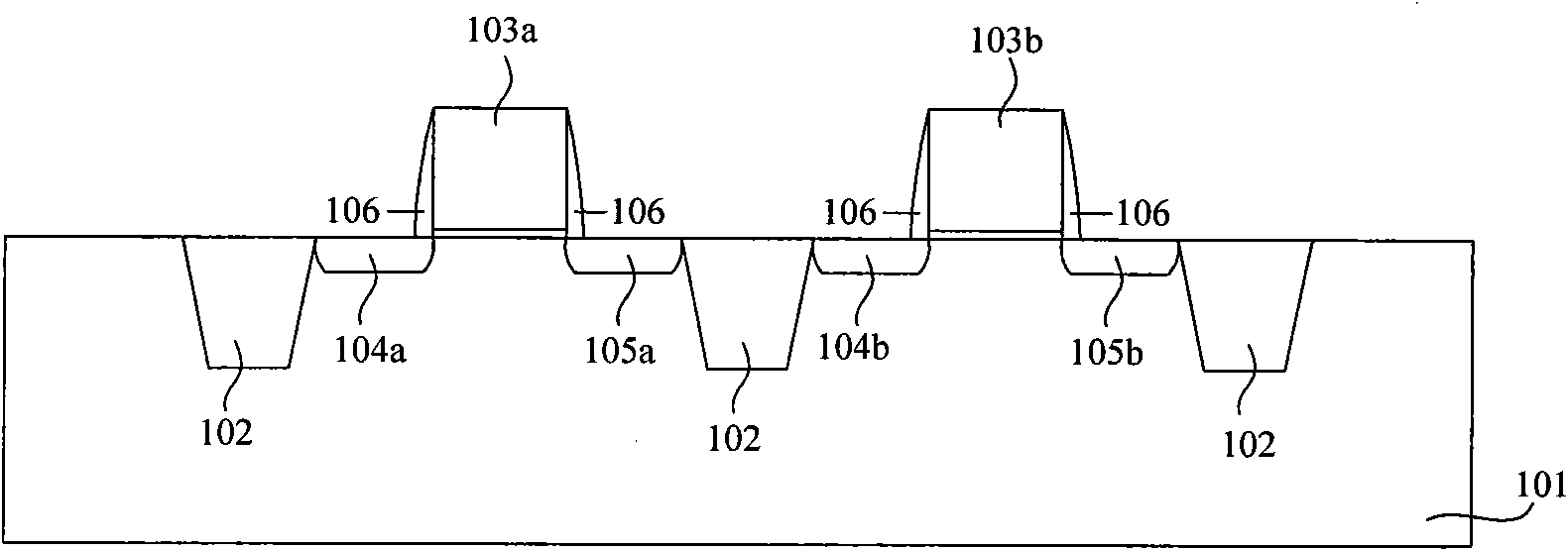

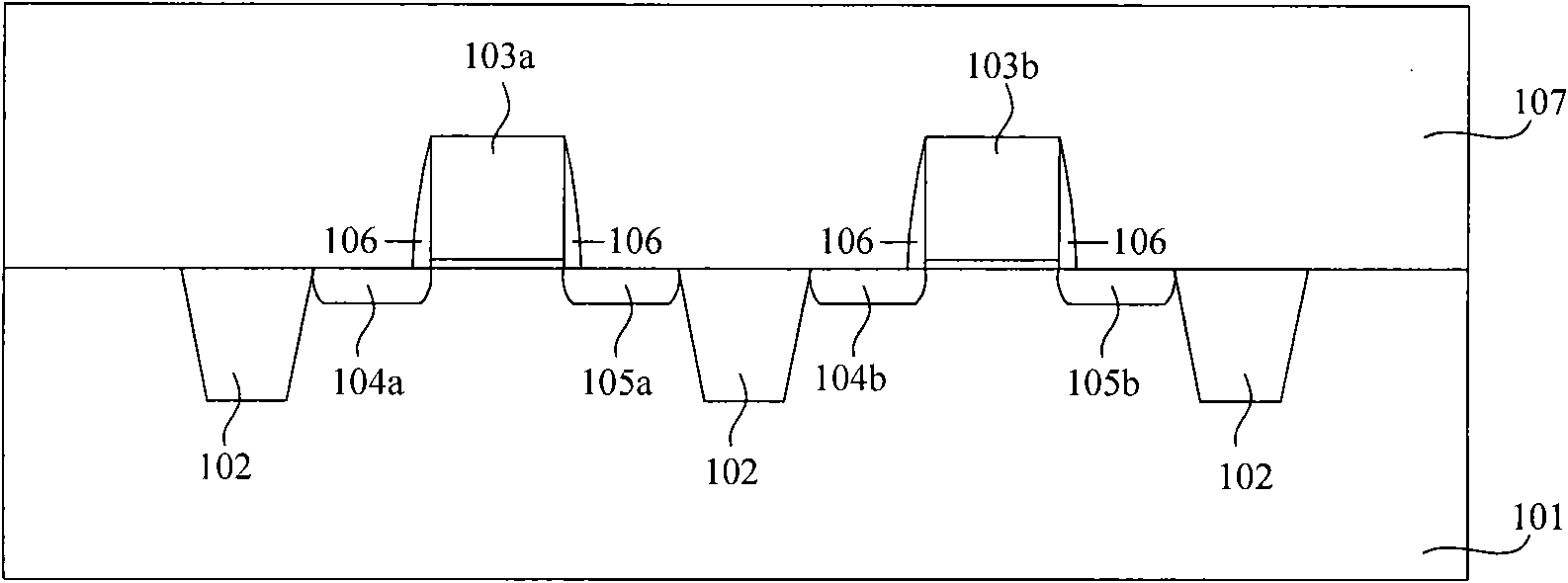

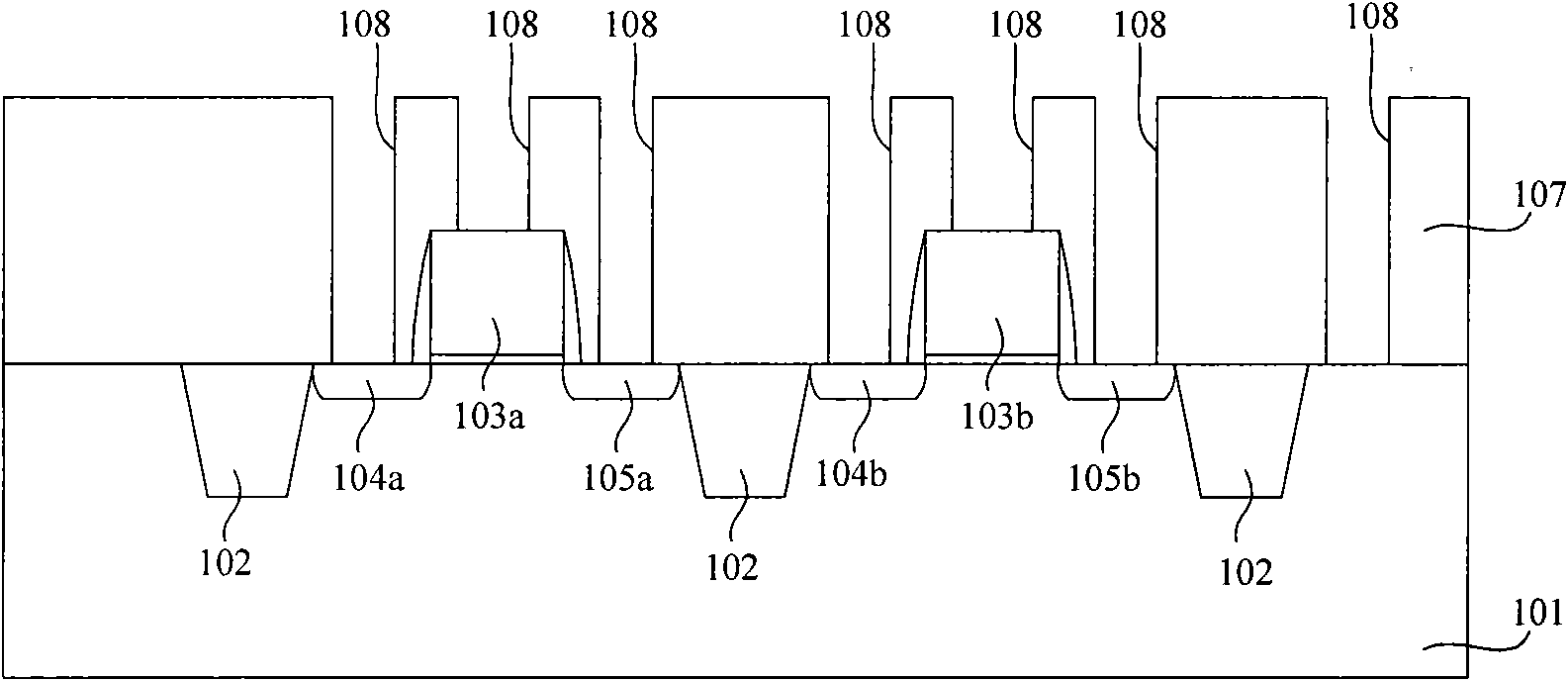

[0033] The following will combine Figure 2A ~ Figure 2I A further detailed description will be made on the method of the present invention for enhancing the pressure resistance capability of chip packaging and the chip thereof.

[0034] The method of the present invention to enhance the pressure resistance capability of chip packaging is to add a pattern for forming a through hole in the redundant area of each metal interlayer insulating layer mask and the redundant area of each metal interconnection mask. The pattern added in the redundant area of the n metal interconnection reticle corresponds to the pattern added in the redundant area of the nth metal interlayer insulating layer reticle, and the redundancy of the n+1 metal interlayer insulating layer reticle The pattern added in the region corresponds to the pattern added in the redundant region of the nth metal interconnection mask, where n=1, 2, 3, . . . , N.

[0035] see Figure 2I The chip of the present inve...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com