SOI wafer-based MEMS structure manufacturing and dicing method

A wafer and dicing technology, applied in the direction of microstructure technology, microstructure devices, processing microstructure devices, etc., can solve the problems of low yield, expensive equipment, high process risk, etc., and achieve high yield, low cost, high efficiency effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

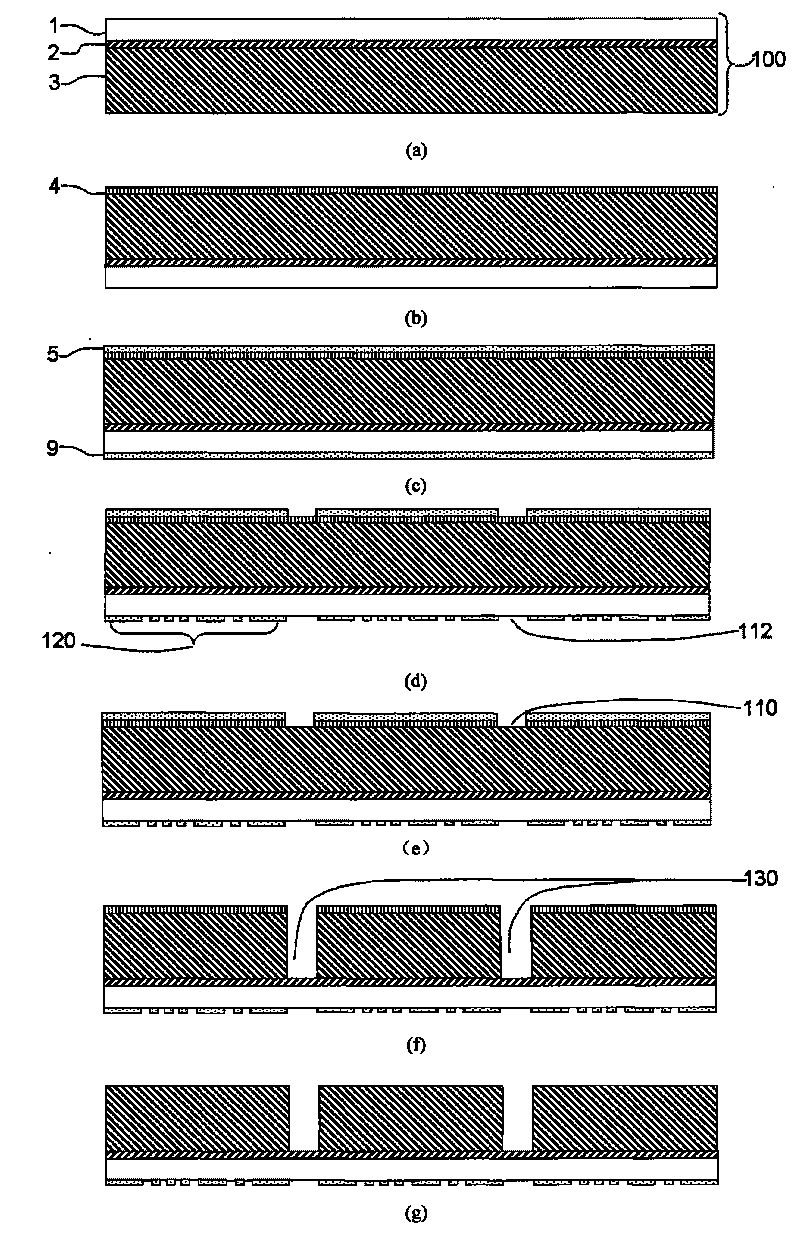

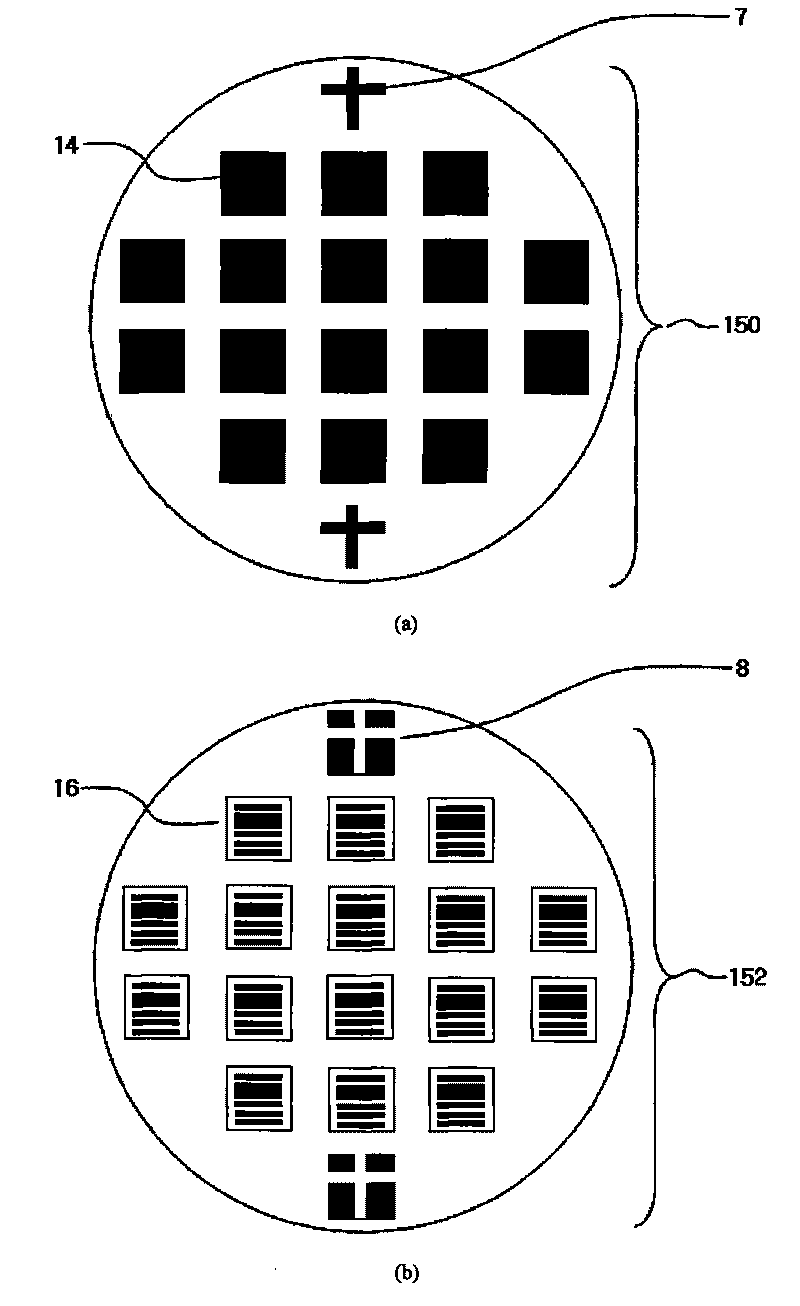

[0040] This embodiment is based on SOI wafer MEMS grating device structure fabrication and dicing method, refer to figure 1 (a)~(k), the structure of the grating device is referred to image 3 , the specific steps are:

[0041] Step 1: Refer to figure 1 (a), cleaning and pre-baking the SOI wafer 100 .

[0042] Step 2: Deposit a deep etch mask layer 4 with a thickness of 500 nm on the surface of the base layer 3. The deep etch mask layer 4 is made of metal aluminum, see figure 1 (b).

[0043] Step 3: Deposit a first photoresist layer 9 with a thickness of 1 μm on the surface of the top layer 1, deposit a second photoresist layer 5 with a thickness of 1 μm on the surface of the deep etching masking layer 4, and bake at a temperature of 110 degrees for 1 minute , see figure 1 (c).

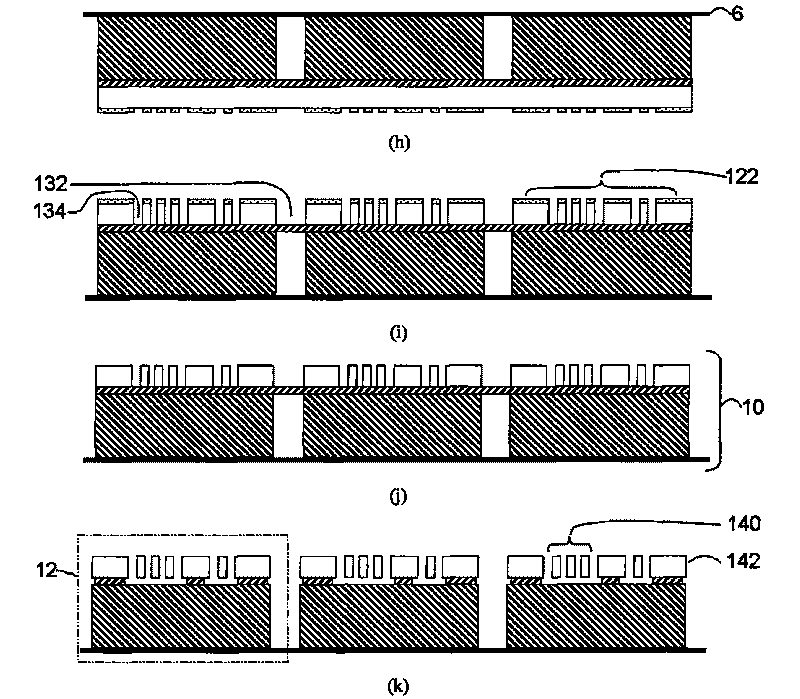

[0044] Step 4: Use the lower mask 150 and the upper mask 152 to perform double-sided photolithography on the wafer processed in step 3. The lower mask 150 and the upper mask 152 have the same ch...

Embodiment 2

[0053] This embodiment is based on SOI wafer MEMS gyroscope device structure fabrication and dicing method, refer to figure 1 (a)~(k), the structure of the gyroscope device is referred to Figure 4 , the specific steps are:

[0054] Step 1: For example figure 1 The SOI wafer 100 shown in (a) is cleaned and prebaked.

[0055] Step 2: Deposit a deep etch mask layer 4 with a thickness of 2 μm on the surface of the base layer 3. The deep etch mask layer 4 is made of silicon dioxide material, see figure 1 (b).

[0056] Step 3: Deposit a 0.9 μm thick first photoresist layer 9 on the surface of the top layer 1, deposit a 0.9 μm thick second photoresist layer 5 on the surface of the deep etching mask layer 4, and heat bake at a temperature of 90 degrees 1 minute, see figure 1 (c).

[0057] Step 4: Use the lower mask 150 and the upper mask 152 to perform double-sided photolithography on the wafer processed in step 3. The lower mask 150 and the upper mask 152 have the same chip un...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com